STMicroelectronics

MK50H27QXX(1997) Datasheet - STMicroelectronics

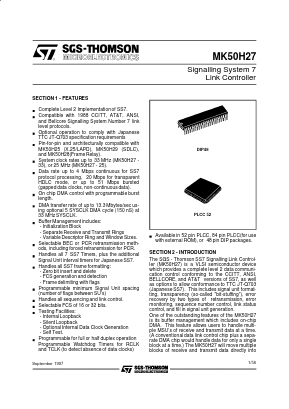

SECTION 2 - INTRODUCTION

The SGS - Thomson SS7 Signalling Link Controller (MK50H27) is a VLSI semiconductor device which provides a complete level 2 data communication control conforming to the CCITT, ANSI, BELLCORE, and AT&T versions of SS7, as well as options to allow conformance to TTC JT-Q703 (Japanese SS7). This includes signal unit formatting, transparency (so-called "bit-stuffing"), error recovery by two types of retransmission, error monitoring, sequence number control, link status control, and fill in signal unit generation.

SECTION 1 - FEATURES

■ Complete Level 2 Implementation of SS7.

■ Compatible with 1988 CCITT, AT&T, ANSI, and Bellcore Signalling System Number 7 link level protocols.

■ Optional operation to comply with Japanese TTC JT-Q703 specification requirements

■ Pin-for-pin and architecturally compatible with MK50H25 (X.25/LAPD), MK50H29 (SDLC), and MK50H28(Frame Relay).

■ System clock rates up to 33 MHz (MK50H27 - 33), or 25 MHz (MK50H27 - 25).

■ Data rate up to 4 Mbps continuous for SS7 protocol processing, 20 Mbps for transparent HDLC mode, or up to 51 Mbps bursted (gapped data clocks, non-continuous data).

■ On chip DMA control with programmable burst length.

■ DMA transfer rate of up to 13.3 Mbytes/sec using optional 5 SYSCLK DMA cycle (150 nS) at 33 MHz SYSCLK.

■ Buffer Management includes:

- Initialization Block

- Separate Receive and Transmit Rings

- Variable Descriptor Ring and Window Sizes.

■ Selectable BEC or PCR retransmission methods, including forced retransmission for PCR.

■ Handles all 7 SS7 Timers, plus the additional

■ Signal Unit interval timers for Japanese SS7.

■ Handles all SS7 frame formatting:

- Zero bit insert and delete

- FCS generation and detection

- Frame delimiting with flags

■ Programmable minimum Signal Unit spacing (number of flags between SU’s)

■ Handles all sequencing and link control.

■ Selectable FCS of 16 or 32 bits.

■ Testing Facilities:

- Internal Loopback

- Silent Loopback

- Optional Internal Data Clock Generation

- Self Test.

■ Programmable for full or half duplex operation Programmable Watchdog Timers for RCLK and TCLK (to detect absence of data clocks)