MITSUBISHI ELECTRIC

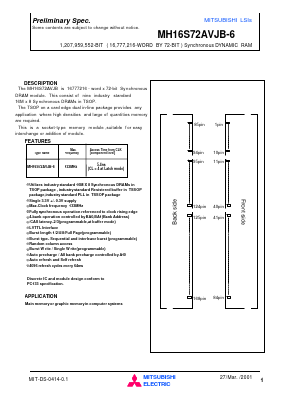

MH16S72AVJB-6 Datasheet - MITSUBISHI ELECTRIC

DESCRIPTION

The MH16S72AVJB is 16777216 - word x 72-bit Synchronous DRAM module. This consist of nine industry standard 16M x 8 Sy nchronous DRAMs in TSOP.

The TSOP on a card edge dual in-line package prov ides any application where high densities and large of quantities memory are required.

This is a socket-ty pe memory module ,suitable f or easy interchange or addition of module.

FEATURES

• Utilizes industry standard 16M X 8 Synchronous DRAMs in TSOP package , industrystandard Resistered buffer in TSSOP package,industry standard PLL in TSSOP package

• Single 3.3V +/- 0.3V supply

• Max.Clock frequency 133MHz

• Fully synchronous operation referenced to clock rising edge

• 4-bank operation controlled byBA0,BA1(Bank Address)

• /CAS latency-2/3(programmable,at buffer mode)

• LVTTL Interface

• Burst length 1/2/4/8/Full Page(programmable)

• Burst type- Sequential and interleave burst (programmable)

• Random column access

• Burst W rite / Single W rite(programmable)

• Auto precharge / All bank precharge controlled by A10

• Auto refresh and Self refresh

• 4096 refresh cycles every 64ms

APPLICATION

Main memoryor graphic memoryin computer systems