Motorola => Freescale

MC92500ZQ Datasheet - Motorola => Freescale

ATM Cell Processor

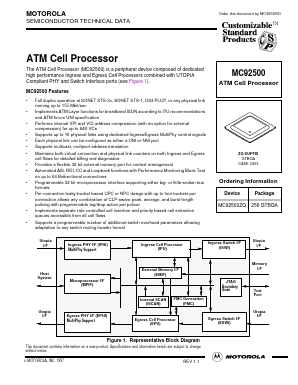

The ATM Cell Processor (MC92500) is a peripheral device composed of dedicated high performance Ingress and Egress Cell Processors combined with UTOPIA Compliant PHY and Switch Interface ports (see Figure 1).

MC92500 Features

• Full duplex operation at SONET STS-3c, SONET STS-1, DS3 PLCP, or any physical link running up to 155 Mbit/sec

• Implements ATM Layer functions for broadband ISDN according to ITU recommendations and ATM forum UNI specification

• Performs internal VPI and VCI address compression (with an option for external compression) for up to 64K VCs

• Supports up to 16 physical links using dedicated Ingress/Egress MultiPhy control signals

• Each physical link can be configured as either a UNI or NNI port

• Supports multicast, multiport address translation

• Maintains both virtual connection and physical link counters on both Ingress and Egress cell flows for detailed billing and diagnostics

• Provides a flexible 32 bit external memory port for context management

• Automated AIS, RDI, CC and Loopback functions with Performance Monitoring Block Test on up to 64 Bidirectional connections

• Programmable 32 bit microprocessor interface supporting either big- or little-endian bus formats

• Per-connection leaky-bucket based UPC or NPC design with up to four buckets per connection allows any combination of CLP-aware peak, average, and burst-length policing with programmable tag/drop action per policer

• Implements separate rate controlled cell insertion and priority based cell extraction queues accessible from all cell flows

• Supports a programmable number of additional switch overhead parameters allowing adaptation to any switch routing header format