Motorola => Freescale

MC1670L Datasheet - Motorola => Freescale

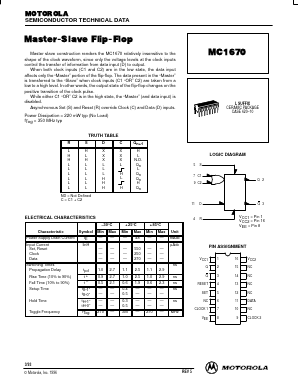

Master-Slave Flip-Flop

Master slave construction renders the MC1670 relatively insensitive to the shape of the clock waveform, since only the voltage levels at the clock inputs control the transfer of information from data input (D) to output.

When both clock inputs (C1 and C2) are in the low state, the data input affects only the “Master” portion of the flip-flop. The data present in the “Master” is transferred to the “Slave” when clock inputs (C1 “OR” C2) are taken from a low to a high level. In other words, the output state of the flip-flop changes on the positive transition of the clock pulse.

While either C1 “OR” C2 is in the high state, the “Master” (and data input) is disabled.

Asynchronous Set (S) and Reset (R) override Clock (C) and Data (D) inputs.

Power Dissipation = 220 mW typ (No Load)

fTog = 350 MHz typ