Fujitsu

MB90522 Datasheet - Fujitsu

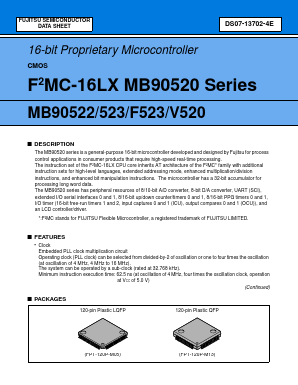

■ DESCRIPTION

The MB90520 series is a general-purpose 16-bit microcontroller developed and designed by Fujitsu for process control applications in consumer products that require high-speed real-time processing.

The instruction set of the F2MC-16LX CPU core inherits AT architecture of the F2MC* family with additional instruction sets for high-level languages, extended addressing mode, enhanced multiplication/division instructions, and enhanced bit manipulation instructions. The microcontroller has a 32-bit accumulator for processing long word data.

The MB90520 series has peripheral resources of 8/10-bit A/D converter, 8-bit D/A converter, UART (SCI), extended I/O serial interfaces 0 and 1, 8/16-bit up/down counter/timers 0 and 1, 8/16-bit PPG timers 0 and 1, I/O timer (16-bit free-run timers 1 and 2, input captures 0 and 1 (ICU), output compares 0 and 1 (OCU)), and an LCD controller/driver.

■ FEATURES

• Clock

Embedded PLL clock multiplication circuit

Operating clock (PLL clock) can be selected from divided-by-2 of oscillation or one to four times the oscillation

(at oscillation of 4 MHz, 4 MHz to 16 MHz).

The system can be operated by a sub-clock (rated at 32.768 kHz).

Minimum instruction execution time: 62.5 ns (at oscillation of 4 MHz, four times the oscillation clock, operation at VCC of 5.0 V)

• Maximum memory space

16 Mbytes

• Instruction set optimized for controller applications

Rich data types (bit, byte, word, long word)

Rich addressing mode (23 types)

Enhanced signed multiplication/division instruction and RETI instruction functions

Enhanced precision calculation realized by 32-bit accumulator

• Instruction set designed for high level language (C) and multi-task operations

Adoption of system stack pointer

Enhanced pointer indirect instructions

Barrel shift instructions

• Program patch function (for two address pointers)

• Enhanced execution speed

4-byte instruction queue

• Enhanced interrupt function

8 levels, 34 factors

• Automatic data transmission function independent of CPU operation

Extended intelligent I/O service function (EI2OS): Up to 16 channels

• Embedded ROM size and types

Mask ROM: 64 kbytes/128 kbytes

Flash ROM: 128 kbytes

• Embedded RAM size

Mask ROM: 4 kbytes

Flash ROM: 4 kbytes

Evaluation product: 6 kbytes

• Low-power consumption (stand-by) mode

Sleep mode (mode in which CPU operating clock is stopped)

Stop mode (mode in which oscillation is stopped)

CPU intermittent operation mode

Hardware stand-by mode

Clock mode (mode in which other than sub-clock and timebase timer are stopped)

• Process

CMOS technology

• I/O port

General-purpose I/O ports (CMOS): 53 ports

General-purpose I/O ports (via pull-up resistors): 24 ports

General-purpose I/O ports (open-drain): 8 ports

Total: 85 ports

• Timer

Timebase timer/watchdog timer: 1 channel

8/16-bit PPG timers 0, 1: 8-bit × 2 channels or 16-bit × 1 channel

• 16-bit re-load timers 0, 1: 2 channels

(Continue ...)