Elpida Memory, Inc

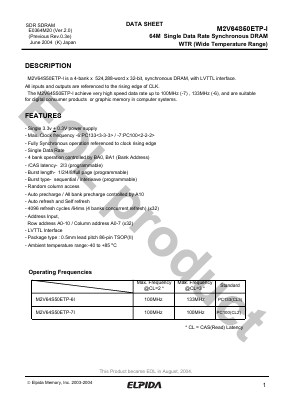

M2V64S50ETP-I Datasheet - Elpida Memory, Inc

DESCRIPTION

M2V64S50ETP-I is a 4-bank x 524,288-word x 32-bit, synchronous DRAM, with LVTTL interface. All inputs and outputs are referenced to the rising edge of CLK.

The M2V64S50ETP-I achieve very high speed data rate up to 100MHz (-7) , 133MHz (-6), and are suitable for digital consumer products or graphic memory in computer systems.

FEATURES

- Single 3.3v + 0.3V power supply

- Max. Clock frequency -6:PC133<3-3-3> / -7:PC100<2-2-2>

- Fully Synchronous operation referenced to clock rising edge

- Single Data Rate

- 4 bank operation controlled by BA0, BA1 (Bank Address)

- /CAS latency- 2/3 (programmable)

- Burst length- 1/2/4/8/full page (programmable)

- Burst type- sequential / interleave (programmable)

- Random column access

- Auto precharge / All bank precharge controlled by A10

- Auto refresh and Self refresh

- 4096 refresh cycles /64ms (4 banks concurrent refresh) (x32)

- Address Input,

Row address A0-10 / Column address A0-7 (x32)

- LVTTL Interface

- Package type : 0.5mm lead pitch 86-pin TSOP(II)

- Ambient temperature range:-40 to +85 oC