STMicroelectronics

M24C32-R_05 Datasheet - STMicroelectronics

SUMMARY DESCRIPTION

These I2C-compatible electrically erasable programmable memory (EEPROM) devices are organized as 8192 x 8 bits (M24C64) and 4096 x 8 bits (M24C32).

I2C uses a two-wire serial interface, comprising a bi-directional data line and a clock line. The devices carry a built-in 4-bit Device Type Identifier code (1010) in accordance with the I2C bus definition. The device behaves as a slave in the I2C protocol, with all memory operations synchronized by the serial clock. Read and Write operations are initiated by a Start condition, generated by the bus master. The Start condition is followed by a Device Select Code and Read/Write bit (RW) (as described in Table 3.), terminated by an acknowl edge bit.

When writing data to the memory, the device inserts an acknowledge bit during the 9th bit time, following the bus master’s 8-bit transmission. When data is read by the bus master, the bus master acknowledges the receipt of the data byte in the same way. Data transfers are terminated by a Stop condition after an Ack for Write, and after a NoAck for Read.

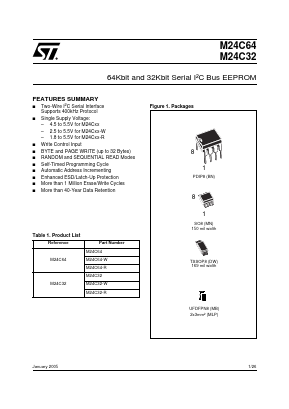

FEATURES SUMMARY

■ Two-Wire I2C Serial Interface Supports 400kHz Protocol

■ Single Supply Voltage:

– 4.5 to 5.5V for M24Cxx

– 2.5 to 5.5V for M24Cxx-W

– 1.8 to 5.5V for M24Cxx-R

■ Write Control Input

■ BYTE and PAGE WRITE (up to 32 Bytes)

■ RANDOM and SEQUENTIAL READ Modes

■ Self-Timed Programming Cycle

■ Automatic Address Incrementing

■ Enhanced ESD/Latch-Up Protection

■ More than 1 Million Erase/Write Cycles

■ More than 40-Year Data Retention