Sharp Electronics

LH540203U-25 Datasheet - Sharp Electronics

FUNCTIONAL DESCRIPTION

The LH540203 is a FIFO (First-In, First-Out) memory device, based on fully-static CMOS dual-port SRAM technology, capable of storing up to 2048 nine-bit words. It follows the industry-standard architecture and package pinouts for nine-bit asynchronous FIFOs. Each nine-bit LH540203 word may consist of a standard eight-bit byte, together with a parity bit or a block-marking/framing bit.

FEATURES

• Fast Access Times: 15/20/25/35/50 ns

• Fast-Fall-Through Time Architecture Based on CMOS Dual-Port SRAM Technology

• Input Port and Output Port Have Entirely Independent Timing

• Expandable in Width and Depth

• Full, Half-Full, and Empty Status Flags

• Data Retransmission Capability

• TTL-Compatible I/O

• Pin and Functionally Compatible with Sharp LH5498 and with Am/IDT/MS7203

• Control Signals Assertive-LOW for Noise Immunity

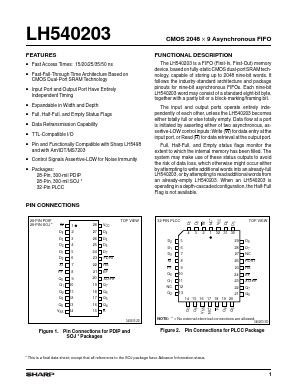

• Packages:

28-Pin, 300-mil PDIP

28-Pin, 300-mil SOJ *

32-Pin PLCC