LOGIC Devices

LF2246 Datasheet - LOGIC Devices

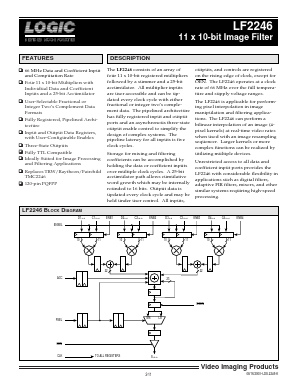

DESCRIPTION

The LF2246 consists of an array of four 11 x 10-bit registered multipliers followed by a summer and a 25-bit accumulator. All multiplier inputs are user accessible and can be updated every clock cycle with either fractional or integer two’s complement data. The pipelined architecture has fully registered input and output ports and an asynchronous three-state output enable control to simplify the design of complex systems. The pipeline latency for all inputs is five clock cycles.

FEATURES

❑ 66 MHz Data and Coefficient Input and Computation Rate

❑ Four 11 x 10-bit Multipliers with Individual Data and Coefficient Inputs and a 25-bit Accumulator

❑ User-Selectable Fractional or Integer Two’s Complement Data Formats

❑ Fully Registered, Pipelined Architecture

❑ Input and Output Data Registers, with User-Configurable Enables

❑ Three-State Outputs

❑ Fully TTL Compatible

❑ Ideally Suited for Image Processing and Filtering Applications

❑ Replaces TRW/Raytheon/Fairchild TMC2246

❑ 120-pin PQFPP