Intel

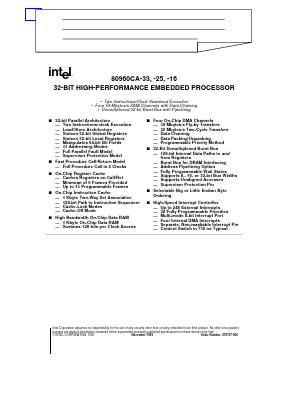

KU80960CA25 Datasheet - Intel

80960CA OVERVIEW

The 80960CA is the second-generation member of the 80960 family of embedded processors. The 80960CA is object code compatible with the 32-bit 80960 Core Architecture while including Special Function Register extensions to control on-chip peripherals and instruction set extensions to shift 64-bit operands and configure on-chip hardware. Multiple 128-bit internal buses, on-chip instruction caching and a sophisticated instruction scheduler allow the processor to sustain execution of two instructions every clock and peak at execution of three instructions per clock.

■ 32-bit Parallel Architecture

— Two Instructions/clock Execution

— Load/Store Architecture

— Sixteen 32-bit Global Registers

— Sixteen 32-bit Local Registers

— Manipulates 64-bit Bit Fields

— 11 Addressing Modes

— Full Parallel Fault Model

— Supervisor Protection Model

■ Fast Procedure Call/Return Model

— Full Procedure Call in 4 Clocks

■ On-Chip Register Cache

— Caches Registers on Call/Ret

— Minimum of 6 Frames Provided

— Up to 15 Programmable Frames

■ On-Chip Instruction Cache

— 1 Kbyte Two-Way Set Associative

— 128-bit Path to Instruction Sequencer

— Cache-Lock Modes

— Cache-Off Mode

■ High Bandwidth On-Chip Data RAM

— 1 Kbyte On-Chip Data RAM

— Sustains 128 bits per Clock Access

■ Four On-Chip DMA Channels

— 59 Mbytes/s Fly-by Transfers

— 32 Mbytes/s Two-Cycle Transfers

— Data Chaining

— Data Packing/Unpacking

— Programmable Priority Method

■ 32-Bit Demultiplexed Burst Bus

— 128-bit Internal Data Paths to and from Registers

— Burst Bus for DRAM Interfacing

— Address Pipelining Option

— Fully Programmable Wait States

— Supports 8-, 16- or 32-bit Bus Widths

— Supports Unaligned Accesses

— Supervisor Protection Pin

■ Selectable Big or Little Endian Byte Ordering

■ High-Speed Interrupt Controller

— Up to 248 External Interrupts

— 32 Fully Programmable Priorities

— Multi-mode 8-bit Interrupt Port

— Four Internal DMA Interrupts

— Separate, Non-maskable Interrupt Pin

— Context Switch in 750 ns Typical