Integrated Device Technology

IDT6178S12PB Datasheet - Integrated Device Technology

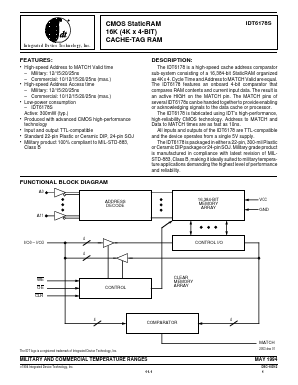

DESCRIPTION:

The IDT6178 is a high-speed cache address comparator sub-system consisting of a 16,384-bit StaticRAM organized as 4K x 4. Cycle Time and Address to MATCH Valid are equal. The IDT6178 features an onboard 4-bit comparator that compares RAM contents and current input data. The result is an active HIGH on the MATCH pin. The MATCH pins of several IDT6178s can be handed together to provide enabling or acknowledging signals to the data cache or processor.

FEATURES:

• High-speed Address to MATCH Valid time

– Military: 12/15/20/25ns

– Commercial: 10/12/15/20/25ns (max.)

• High-speed Address Access time

– Military: 12/15/20/25ns

– Commercial: 10/12/15/20/25ns (max.)

• Low-power consumption

– IDT6178S

Active: 300mW (typ.)

• Produced with advanced CMOS high-performance technology

• Input and output TTL-compatible

• Standard 22-pin Plastic or Ceramic DIP, 24-pin SOJ

• Military product 100% compliant to MIL-STD-883, Class B