Integrated Circuit Systems

ICS620-01RT Datasheet - Integrated Circuit Systems

Description

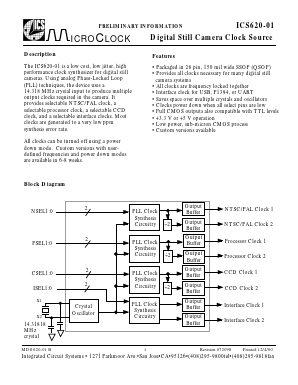

The ICS620-01 is a low cost, low jitter, high performance clock synthesizer for digital still cameras. Using analog Phase-Locked Loop (PLL) techniques, the device uses a 14.318 MHz crystal input to produce multiple output clocks required in the camera. It provides selectable NTSC/PAL clock, a selectable processor clock, a selectable CCD clock, and a selectable interface clocks. Most clocks are generated to a very low ppm synthesis error rate.

FEATUREs

• Packaged in 28 pin, 150 mil wide SSOP (QSOP)

• Provides all clocks necessary for many digital still camera systems

• All clocks are frequency locked together

• Interface clock for USB, P1394, or UART

• Saves space over multiple crystals and oscillators

• Clocks power down when all select pins are low

• Full CMOS outputs also compatible with TTL levels

• +3.3 V or +5 V operation

• Low power, sub-micron CMOS process

• Custom versions available