NXP Semiconductors.

HEF40175B Datasheet - NXP Semiconductors.

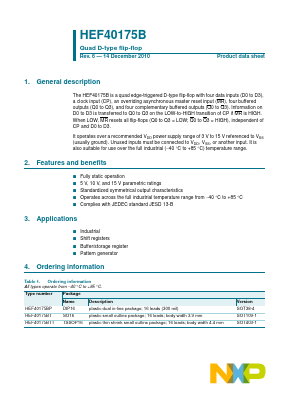

General description

The HEF40175B is a quad edge-triggered D-type flip-flop with four data inputs (D0 to D3), a clock input (CP), an overriding asynchronous master reset input (MR), four buffered outputs (Q0 to Q3), and four complementary buffered outputs (Q0 to Q3). Information on D0 to D3 is transferred to Q0 to Q3 on the LOW-to-HIGH transition of CP if MR is HIGH. When LOW, MR resets all flip-flops (Q0 to Q3 = LOW; Q0 to Q3 = HIGH), independent of CP and D0 to D3.

FEATUREs and benefits

■ Fully static operation

■ 5 V, 10 V, and 15 V parametric ratings

■ Standardized symmetrical output characteristics

■ Operates across the full industrial temperature range from -40°C to +85°C

■ Complies with JEDEC standard JESD 13-B

APPLICATIONs

■ Industrial

■ Shift registers

■ Buffer/storage register

■ Pattern generator