Intersil

HCS160D/SAMPLE Datasheet - Intersil

Description

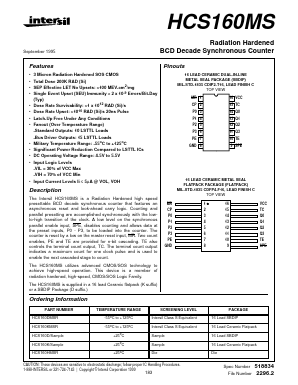

The Intersil HCS160MS is a Radiation Hardened high speed presettable BCD decade synchronous counter that features an asynchronous reset and look-ahead carry logic. Counting and parallel presetting are accomplished synchronously with the lowto-high transition of the clock. A low level on the synchronous parallel enable input, SPE, disables counting and allows data at the preset inputs, P0 - P3, to be loaded into the counter. The counter is reset by a low on the master reset input, MR. Two count enables, PE and TE are provided for n-bit cascading. TE also controls the terminal count output, TC. The terminal count output indicates a maximum count for one clock pulse and is used to enable the next cascaded stage to count.

FEATUREs

• 3 Micron Radiation Hardened SOS CMOS

• Total Dose 200K RAD (Si)

• SEP Effective LET No Upsets: >100 MEV-cm2/mg

• Single Event Upset (SEU) Immunity < 2 x 10-9 Errors/Bit-Day (Typ)

• Dose Rate Survivability: >1 x 1012 RAD (Si)/s

• Dose Rate Upset: >1010 RAD (Si)/s 20ns Pulse

• Latch-Up Free Under Any Conditions

• Fanout (Over Temperature Range)

-Standard Outputs: 10 LSTTL Loads

-Bus Driver Outputs: 15 LSTTL Loads

• Military Temperature Range: -55°C to +125°C

• Significant Power Reduction Compared to LSTTL ICs

• DC Operating Voltage Range: 4.5V to 5.5V

• Input Logic Levels

-VIL = 30% of VCC Max

-VIH = 70% of VCC Min

• Input Current Levels Ii ≤ 5µA @ VOL, VOH