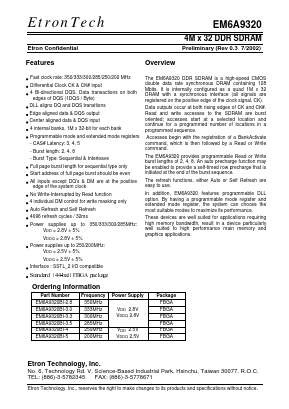

Etron Technology

EM6A9320BI-33 Datasheet - Etron Technology

Overview

The EM6A9320 DDR SDRAM is a high-speed CMOS double data rate synchronous DRAM containing 128 Mbits. It is internally configured as a quad 1M x 32 DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal, CK).

Features

• Fast clock rate: 350/333/300/285/250/200 MHz

• Differential Clock CK & CK# input

• 4 Bi-directional DQS. Data transactions on both

edges of DQS (1DQS / Byte)

• DLL aligns DQ and DQS transitions

• Edge aligned data & DQS output

• Center aligned data & DQS input

• 4 internal banks, 1M x 32-bit for each bank

• Programmable mode and extended mode registers

- CAS# Latency: 3, 4, 5

- Burst length: 2, 4, 8

- Burst Type: Sequential & Interleave

• Full page burst length for sequential type only

• Start address of full page burst should be even

• All inputs except DQ’s & DM are at the positive

edge of the system clock

• No Write-Interrupted by Read function

• 4 individual DM control for write masking only

• Auto Refresh and Self Refresh

• 4096 refresh cycles / 32ms

• Power supplies up to 350/333/300/285MHz:

VDD = 2.8V ± 5%

VDDQ = 2.8V ± 5%

• Power supplies up to 250/200MHz:

VDD = 2.5V ± 5%

VDDQ = 2.5V ± 5%

• Interface : SSTL_2 I/O compatible

• Standard 144-ball FBGA package