Cypress Semiconductor

CY7C480XV25-200 Datasheet - Cypress Semiconductor

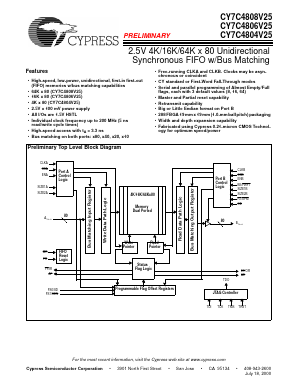

Features

• High-speed, low-power, unidirectional, first-in first-out (FIFO) memories w/bus matching capabilities

• 64K x 80 (CY7C4808V25)

• 16K x 80 (CY7C4806V25)

• 4K x 80 (CY7C4804V25)

• 2.5V ± 100 mV power supply

• All I/Os are 1.5V HSTL

• Individual clock frequency up to 200 MHz (5 ns read/write cycle times)

• High-speed access with tA = 3.3 ns

• Bus matching on both ports: x80, x40, x20, x10

• Free-running CLKA and CLKB. Clocks may be asynchronous or coincident

• CY standard or First-Word Fall-Through modes

• Serial and parallel programming of Almost Empty/Full flags, each with 3 default values (8, 16, 64)

• Master and Partial reset capability

• Retransmit capability

• Big or Little Endian format on Port B

• 288 FBGA 19 mm x 19 mm (1.0-mm ball pitch) packaging

• Width and depth expansion capability

• Fabricated using Cypress 0.21-micron CMOS Technology for optimum speed/power