Analog Devices

ADSP-21061LKB-176 Datasheet - Analog Devices

GENERAL DESCRIPTION

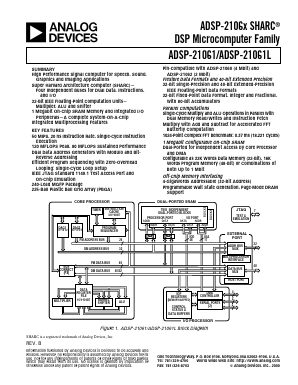

The ADSP-21061 is a member of the powerful SHARC family of floating point processors. The SHARC—Super Harvard Architecture Computer—are signal processing microcomputers that offer new capabilities and levels of integration and performance. The ADSP-21061 is a 32-bit processor optimized for high performance DSP applications. The ADSP-21061 combines the ADSP-21000 DSP core with a dual-ported on-chip SRAM and an I/O processor with a dedicated I/O bus to form a complete system-in-a-chip.

SUMMARY

High Performance Signal Computer for Speech, Sound, Graphics and Imaging Applications

Super Harvard Architecture Computer (SHARC)— Four Independent Buses for Dual Data, Instructions, and I/O

32-Bit IEEE Floating-Point Computation Units— Multiplier, ALU and Shifter

1 Megabit On-Chip SRAM Memory and Integrated I/O Peripherals—A Complete System-On-A-Chip

Integrated Multiprocessing Features

KEY FEATURES

50 MIPS, 20 ns Instruction Rate, Single-Cycle Instruction Execution

120 MFLOPS Peak, 80 MFLOPS Sustained Performance

Dual Data Address Generators with Modulo and Bit Reverse Addressing

Efficient Program Sequencing with Zero-Overhead Looping: Single-Cycle Loop Setup

IEEE JTAG Standard 1149.1 Test Access Port and On-Chip Emulation

240-Lead MQFP Package

225-Ball Plastic Ball Grid Array (PBGA)

Pin-Compatible with ADSP-21060 (4 Mbit) and ADSP-21062 (2 Mbit)

Flexible Data Formats and 40-Bit Extended Precision

32-Bit Single-Precision and 40-Bit Extended-Precision IEEE Floating-Point Data Formats

32-Bit Fixed-Point Data Format, Integer and Fractional, with 80-Bit Accumulators