Analog Devices

AD9552(RevC) Datasheet - Analog Devices

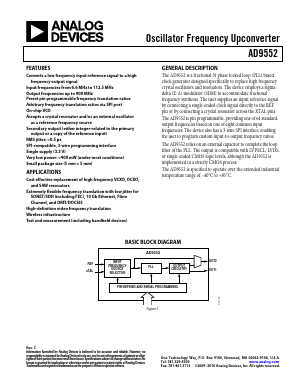

GENERAL DESCRIPTION

The AD9552 is a fractional-N phase locked loop (PLL) based clock generator designed specifically to replace high frequency crystal oscillators and resonators. The device employs a sigma-delta (Σ-Δ) modulator (SDM) to accommodate fractional frequency synthesis. The user supplies an input reference signal by connecting a single-ended clock signal directly to the REF pin or by connecting a crystal resonator across the XTAL pins.

FEATURES

Converts a low frequency input reference signal to a high

frequency output signal

Input frequencies from 6.6 MHz to 112.5 MHz

Output frequencies up to 900 MHz

Preset pin programmable frequency translation ratios

Arbitrary frequency translation ratios via SPI port

On-chip VCO

Accepts a crystal resonator and/or an external oscillator

as a reference frequency source

Secondary output (either integer-related to the primary

output or a copy of the reference input)

RMS jitter: <0.5 ps

SPI-compatible, 3-wire programming interface

Single supply (3.3 V)

Very low power: <400 mW (under most conditions)

Small package size (5 mm × 5 mm)

APPLICATIONS

Cost effective replacement of high frequency VCXO, OCXO,

and SAW resonators

Extremely flexible frequency translation with low jitter for

SONET/SDH (including FEC), 10 Gb Ethernet, Fibre

Channel, and DRFI/DOCSIS

High-definition video frequency translation

Wireless infrastructure

Test and measurement (including handheld devices)