Analog Devices

AD9547BCPZ-REEL7(Rev0) Datasheet - Analog Devices

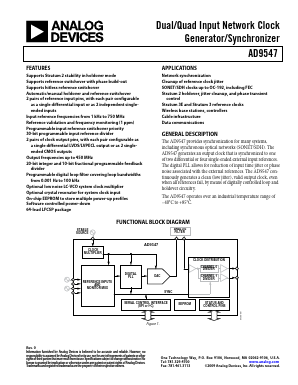

GENERAL DESCRIPTION

The AD9547 provides synchronization for many systems, including synchronous optical networks (SONET/SDH). The AD9547 generates an output clock that is synchronized to one of two differential or four single-ended external input references. The digital PLL allows for reduction of input time jitter or phase noise associated with the external references. The AD9547 continuously generates a clean (low jitter), valid output clock, even when all references fail, by means of digitally controlled loop and holdover circuitry.

The AD9547 operates over an industrial temperature range of −40°C to +85°C.

FEATURES

Supports Stratum 2 stability in holdover mode

Supports reference switchover with phase build-out

Supports hitless reference switchover

Automatic/manual holdover and reference switchover

2 pairs of reference input pins, with each pair configurable

as a single differential input or as 2 independent single-ended inputs

Input reference frequencies from 1 kHz to 750 MHz

Reference validation and frequency monitoring (1 ppm)

Programmable input reference switchover priority

30-bit programmable input reference divider

2 pairs of clock output pins, with each pair configurable as

a single differential LVDS/LVPECL output or as 2 single-ended CMOS outputs

Output frequencies up to 450 MHz

20-bit integer and 10-bit fractional programmable feedback

divider

Programmable digital loop filter covering loop bandwidths

from 0.001 Hz to 100 kHz

Optional low noise LC-VCO system clock multiplier

Optional crystal resonator for system clock input

On-chip EEPROM to store multiple power-up profiles

Software controlled power-down

64-lead LFCSP package

APPLICATIONS

Network synchronization

Cleanup of reference clock jitter

SONET/SDH clocks up to OC-192, including FEC

Stratum 2 holdover, jitter cleanup, and phase transient

control

Stratum 3E and Stratum 3 reference clocks

Wireless base stations, controllers

Cable infrastructure

Data communications