STMicroelectronics

74LVQ374(2001) Datasheet - STMicroelectronics

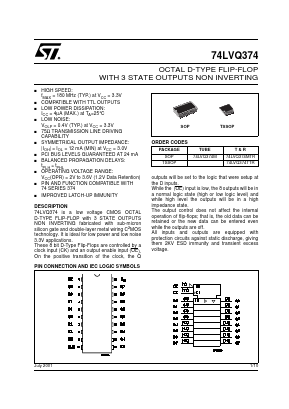

DESCRIPTION

74LVQ374 is a low voltage CMOS OCTAL D-TYPE FLIP-FLOP with 3 STATE OUTPUTS NON INVERTING fabricated with sub-micron silicon gate and double-layer metal wiring C2MOS technology. It is ideal for low power and low noise 3.3V applications.

These 8 bit D-Type Flip-Flops are controlled by a clock input (CK) and an output enable input (OE). On the positive transition of the clock, the Q outputs will be set to the logic that were setup at the D inputs.

While the (OE) input is low, the 8 outputs will be in a normal logic state (high or low logic level) and while high level the outputs will be in a high impedance state.

The output control does not affect the internal operation of flip-flops; that is, the old data can be retained or the new data can be entered even while the outputs are off.

All inputs and outputs are equipped with protection circuits against static discharge, giving them 2KV ESD immunity and transient excess voltage.

■ HIGH SPEED:

fMAX = 180 MHz (TYP.) at VCC = 3.3V

■ COMPATIBLE WITH TTL OUTPUTS

■ LOW POWER DISSIPATION:

ICC = 4µA (MAX.) at TA=25°C

■ LOW NOISE:

VOLP = 0.4V (TYP.) at VCC = 3.3V

■ 75Ω TRANSMISSION LINE DRIVING CAPABILITY

■ SYMMETRICAL OUTPUT IMPEDANCE:

|IOH| = IOL = 12 mA (MIN) at VCC = 3.0V

■ PCI BUS LEVELS GUARANTEED AT 24 mA

■ BALANCED PROPAGATION DELAYS: tPLH ≅ tPHL

■ OPERATING VOLTAGE RANGE:

VCC(OPR) = 2V to 3.6V (1.2V Data Retention)

■ PIN AND FUNCTION COMPATIBLE WITH 74 SERIES 374

■ IMPROVED LATCH-UP IMMUNITY