White Electronic Designs => Micro Semi

5962-9761201HXX Datasheet - White Electronic Designs => Micro Semi

FEATURES

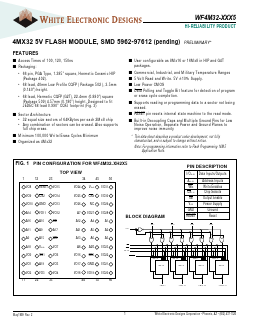

■ Access Times of 100, 120, 150ns

■ Packaging:

• 66 pin, PGA Type, 1.385" square, Hermetic Ceramic HIP (Package 402).

• 68 lead, 40mm Low Profile CQFP ( Package 502 ), 3.5mm (0.140") height.

• 68 lead, Hermetic CQFP (G2T), 22.4mm (0.880") square (Package 509) 4.57mm (0.180") height. Designed to fit JEDEC 68 lead 0.990" CQFJ footprint (Fig. 3)

■ Sector Architecture

• 32 equal size sectors of 64KBytes per each 2Mx8 chip

• Any combination of sectors can be erased. Also supports full chip erase.

■ Minimum 100,000 Write/Erase Cycles Minimum

■ Organized as 4Mx32

■ User configurable as 8Mx16 or 16Mx8 in HIP and G4T packages.

■ Commercial, Industrial, and Military Temperature Ranges

■ 5 Volt Read and Write. 5V ± 10% Supply.

■ Low Power CMOS

■ Data Polling and Toggle Bit feature for detection of program or erase cycle completion.

■ Supports reading or programming data to a sector not being erased.

■ RESET pin resets internal state machine to the read mode.

■ Built-in Decoupling Caps and Multiple Ground Pins for Low Noise Operation, Separate Power and Ground Planes to improve noise immunity