Data Delay Devices

3D7105Z Datasheet - Data Delay Devices

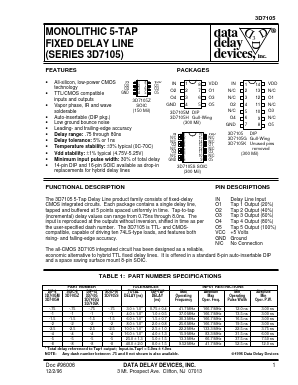

FUNCTIONAL DESCRIPTION

The 3D7105 5-Tap Delay Line product family consists of fixed-delay CMOS integrated circuits. Each package contains a single delay line, tapped and buffered at 5 points spaced uniformly in time. Tap-to-tap (incremental) delay values can range from 0.75ns through 8.0ns. The input is reproduced at the outputs without inversion, shifted in time as per the user-specified dash number. The 3D7105 is TTL- and CMOS-compatible, capable of driving ten 74LS-type loads, and features both rising- and falling-edge accuracy.

FEATURES

• All-silicon, low-power CMOS technology

• TTL/CMOS compatible inputs and outputs

• Vapor phase, IR and wave solderable

• Auto-insertable (DIP pkg.)

• Low ground bounce noise

• Leading- and trailing-edge accuracy

• Delay range: .75 through 80ns

• Delay tolerance: 5% or 1ns

• Temperature stability: ±3% typical (0C-70C)

• Vdd stability: ±1% typical (4.75V-5.25V)

• Minimum input pulse width: 30% of total delay

• 14-pin DIP and 16-pin SOIC available as drop-in replacements for hybrid delay lines