# 78Q8430 10/100 Ethernet MAC and PHY

Simplifying System Integration TM

#### **DATA SHEET**

March 2009

#### **DESCRIPTION**

The Teridian 78Q8430 is a 10/100 Fast Ethernet controller supporting multi-media offload. The device is optimized for host processor offloading and throughput enhancements for demanding multi-media applications found in Set Top Box, IP Video and Broadband Media Appliance applications. The 78Q8430 seamlessly interfaces to non-PCI processors through a simplified pseudo SRAM-like Host Bus Interface supporting 32/16/8 bit data bus widths. Supported features include IEEE802.3x flow control and full IEEE802.3 and 802.3u standards compliance.

Supporting 10Base-T and 100Base-TX, the transceiver provides Auto MDI-X cable cross-over correction, AUTO Negotiation, Link Configuration and full/half duplex support with full duplex flow control. The line interface requires only a dual 1:1 isolation transformer. Numerous packet processing and IP address resolution control functions are incorporated, including an extensive set of Error Monitoring, Reporting and Troubleshooting features. The 78Q8430 provides optimal 10/100 Ethernet connectivity in demanding video streaming and mixed-media applications.

#### **BENEFITS**

- Support for IEEE-802.3, IEEE-802.3u and IEEE-802.3-2000 Annex 31.B

- Low host CPU utilization/overhead with minimal software driver overhead and small driver memory space requirements

- Improved packet processing, low latency and low host CPU utilization

- · Highest performance streaming Video over IP

- Optimized performance in mixed media application such as video, data and voice

- Ease of use, faster development cycles, high throughput

- Optimized power conservation with automatic turn on when needed

- · Reduced host CPU utilization and overhead

- Improved packet processing

- Optimized performance in mixed media applications

#### **FEATURES**

- Single chip 10Base-T/100Base-TX IEEE-802.3 compliant MAC and PHY

- Adaptive 32 kB SRAM FIFO memory allocation between Tx and Rx paths

- Queue independent user settable water marks

- Per queue status indication

- Address Resolution Controller (ARC)

- Multiple perfect address filtering: 8 default (max 12)

- Wildcard address filtering, individual, multicast and broadcast address recognition and filtering

- Positive/negative filtering and promiscuous mode

- 64 kB JUMBO packet support

- QoS: 4 Transmit priority levels

- Non-PCI pseudo-SRAM Host Bus Interface

- 8-bit, 16-bit and 32-bit bus width

- Big/little endian support for 16-bit/32-bit bus widths

- Asynchronous (100 MHz) and synchronous (50 MHz) bus clock support

- Low power and flexible power supply management

- Power down/save

- Wake on LAN (Magic Packet<sup>™</sup>, OnNow packet)

- Link status change

- Traffic Offload Engine Functionality

- Transfer frame: APF & ICMP Echo

- IP Firewall configuration: drop frames on source IP address

- IP Checksum

- Available in an industrial temperature range (-40 °C to +85 °C)

- RoHS compliant (6/6) lead-free package

#### **APPLICATIONS**

- Satellite, cable and IPTV Set Top Boxes

- Multi Media Residential Gateways

- High Definition 1080p/1080i DTVs

- IP-PVR and video distribution systems

- Digital Video Recorders/Players

- Routers and IADs

- Video over IP system, IP-PBX

- IP Security Cameras / PVRs

- Low latency industrial automation

# **Table of Contents**

| 1 | Intro | oduction                                   |    |

|---|-------|--------------------------------------------|----|

|   | 1.1   | Systems Applications                       |    |

|   | 1.2   | System Level Application Information       |    |

|   |       | 1.2.1 Set Top Box Application              |    |

|   |       | 1.2.2 IP Security Application              |    |

|   |       | 1.2.3 IP PBX Application                   |    |

|   | 1.3   | Overview                                   |    |

|   | 1.4   | Application Environments                   |    |

|   | 1.5   | Supply Voltages                            | 1( |

|   | 1.6   | Power Management                           |    |

| 2 | Pinc  | out                                        | 11 |

| 3 | Pin l | Description                                | 12 |

|   | 3.1   | Pin Legend                                 | 12 |

|   | 3.2   | Pin Descriptions                           |    |

|   |       | 3.2.1 Clock Pins                           | 12 |

|   |       | 3.2.2 Media Dependent Interface (MDI) Pins | 13 |

|   |       | 3.2.3 LED Display (PHY) Pins               | 13 |

|   |       | 3.2.4 EEPROM Pins                          |    |

|   |       | 3.2.5 GBI Data Pins                        |    |

|   |       | 3.2.6 GBI Address Pins                     |    |

|   |       | 3.2.7 GBI Control Pins                     |    |

|   |       | 3.2.8 Mode Pins                            |    |

|   |       | 3.2.9 JTAG Pins                            |    |

|   |       | 3.2.10 Power Pins                          |    |

| 4 | Elec  | ctrical Specification                      | 18 |

|   | 4.1   | Absolute Maximum Ratings                   |    |

|   | 4.2   | Recommended Operation Conditions           |    |

|   | 4.3   | DC Characteristics                         |    |

|   | 4.4   | Digital I/O Characteristics                |    |

|   | 4.5   | Analog Electrical Characteristics          |    |

|   |       | 4.5.1 100Base-TX Transmitter               |    |

|   |       | 4.5.2 100Base-TX Transmitter (Informative) |    |

|   |       | 4.5.3 100Base-TX Receiver                  |    |

|   |       | 4.5.4 10Base-T Transmitter                 |    |

|   |       | 4.5.5 10Base-T Transmitter (Informative)   |    |

| _ |       |                                            |    |

| 5 | Hos   | t Interface Timing Specification           |    |

|   | 5.1   | Host Interface                             |    |

|   |       | 5.1.1 Synchronous Mode Timing              |    |

|   |       | 5.1.2 Bus Clock Timing                     |    |

|   |       | 5.1.3 Reset Timing                         |    |

| 6 | Fund  | ctional Description                        | 25 |

|   | 6.1   | Internal Block Diagrams                    |    |

|   |       | 6.1.1 Internal Digital Block               | 25 |

|   |       | 6.1.2 Internal PHY                         |    |

|   | 6.2   | Data Queuing                               |    |

|   | 6.3   | Host Interface                             |    |

|   |       | 6.3.1 Reading Receive Data                 |    |

|   |       | 6.3.2 Writing Transmit Data                |    |

|   | 0.4   | 6.3.3 DMA Slave Mode Access                |    |

|   | 6.4   | Snoop Mode Access                          |    |

|   | 6.5   | Water Marking                              |    |

|   |       | 6.5.1 Interrupt Watermark                  | 30 |

|   |                        | 6.5.2 PAUSE Watermark                                   | 30 |

|---|------------------------|---------------------------------------------------------|----|

|   |                        | 6.5.3 Headroom Watermark                                | 30 |

|   | 6.6                    | Counters                                                | 30 |

|   |                        | 6.6.1 Summary of Counters                               |    |

|   |                        | 6.6.2 Reading and Setting Counter Values                |    |

|   |                        | 6.6.3 Precision Counting                                |    |

|   |                        | 6.6.4 Rollover Interrupts                               |    |

|   | 6.7                    | Packet Classification                                   |    |

|   |                        | 6.7.1 Address Filtering                                 |    |

|   |                        | 6.7.2 Configuring the CAM                               |    |

|   |                        | 6.7.4 Default CAM Rule Summary                          |    |

|   | 6.8                    | Timers                                                  |    |

|   | 0.0                    | 6.8.1 PAUSE Timer                                       |    |

|   |                        | 6.8.2 HNR Timer                                         |    |

|   |                        | 6.8.3 Interrupt Delay Timer                             |    |

|   | 6.9                    | EEPROM Controller                                       |    |

|   |                        | Ethernet MAC                                            |    |

|   |                        | 6.10.1 MAC Transmit Block                               |    |

|   |                        | 6.10.2 MAC Receive Block                                |    |

|   |                        | 6.10.3 MAC Control Register                             |    |

|   |                        | 6.10.4 Transmitting a Frame                             | 45 |

|   |                        | 6.10.5 IEEE 802.3 Transmit Protocols                    | 45 |

|   |                        | 6.10.6 Transmit Operation                               | 46 |

|   |                        | 6.10.7 Receiving a Frame                                |    |

|   |                        | 6.10.8 Strip Padding/FCS                                |    |

|   | 6.11                   | MAC Error Reporting                                     |    |

|   |                        | 6.11.1 MAC Transmit Errors                              |    |

|   |                        | 6.11.2 MAC Receive Errors                               |    |

|   | 6.12                   | PHY Operations                                          | 49 |

|   |                        | 6.12.1 Automatic MDI/MDIX Cable Crossover Configuration |    |

|   |                        | 6.12.2 100Base-TX Transmit                              |    |

|   |                        | 6.12.3 100Base-TX Receive                               |    |

|   |                        | 6.12.4 10Base-T Transmit                                |    |

|   |                        | 6.12.6 SQE Test                                         |    |

|   |                        | 6.12.7 Polarity Correction                              |    |

|   |                        | 6.12.8 Natural Loopback                                 |    |

|   |                        | 6.12.9 Auto-Negotiation                                 |    |

|   |                        | 6.12.10 LED Indicators                                  |    |

|   |                        | 6.12.11 PHY Interrupts                                  |    |

|   |                        | 6.12.12 Internal Clock PLL                              |    |

| 7 | Doa:                   | ster Descriptions                                       |    |

| 1 | _                      |                                                         |    |

|   | 7.1                    | Register Overview                                       |    |

|   | 7.2                    | QUE Register Overview                                   |    |

|   | 7.3<br>7.4             | CTL Register Overview                                   |    |

|   | 7. <del>4</del><br>7.5 | QUE Registers                                           |    |

|   | 1.5                    | 7.5.1 Packet Control Word Register                      |    |

|   |                        | 7.5.2 Packet Size Register                              |    |

|   |                        | 7.5.3 Setup Transmit Data Register                      |    |

|   |                        | 7.5.4 Transmit Data Register                            |    |

|   |                        | 7.5.5 Receive Data Register                             |    |

|   |                        | 7.5.6 QUE First/Last Register                           |    |

|   |                        | 7.5.7 QUE Status Register                               |    |

|   | 7.6                    | CTL Registers                                           |    |

|   |                        | 7.6.1 DMA Control and Status Register                   |    |

|   |                        | 7.6.2 Receive Packet Status Register                    |    |

| 10 | Cyst  |        |                                                          |                      |

|----|-------|--------|----------------------------------------------------------|----------------------|

|    | Syste | em Bus | Interface Schematic                                      | . 84                 |

| 9  |       |        | Crystal                                                  |                      |

|    |       |        |                                                          |                      |

| 8  | Isola |        | ansformers                                               |                      |

|    |       |        | PHY MDI / MDIX Control Register – MR24                   |                      |

|    |       |        | PHY LED Configuration Register – MR23                    |                      |

|    |       |        | PHY Diagnostic Register – MR18                           |                      |

|    |       |        | PHY Transceiver Control Register – MR19                  |                      |

|    |       |        | PHY Interrupt Control / Status Register – MR17           |                      |

|    |       |        | PHY Vendor Specific Register – MR16                      |                      |

|    |       | 7.7.7  | PHY Auto-Negotiation Expansion Register – MR6            | . 78<br>. 78         |

|    |       | 7.7.6  | PHY Auto-Negotiation Line Partner Ability Register – MR5 | . <i>, ,</i><br>. 78 |

|    |       | 7.7.5  | PHY Auto-Negotiation Advertisement Registers – MR4       | . , ,<br>. 77        |

|    |       |        | PHY Identifier Registers – MR2, MR3                      |                      |

|    |       |        | PHY Status Register – MR1                                |                      |

|    |       |        | PHY Control Register – MR0                               |                      |

|    | 1.1   | 7.7.1  | PHY Register Overview                                    |                      |

|    | 7.7   |        | anagement Registers                                      |                      |

|    |       |        | Host Interrupt Mask Register                             |                      |

|    |       |        | Receive RMON Mask Register  Host Interrupt Register      |                      |

|    |       |        | Receive RMON Interrupt Register                          |                      |

|    |       |        | Transmit RMON Mask Register                              |                      |

|    |       |        | Transmit RMON Interrupt Register                         |                      |

|    |       |        | Overflow/Underrun Mask Register                          |                      |

|    |       |        | Overflow/Underrup Meek Register                          |                      |

|    |       |        | Que Status Mask Register                                 |                      |

|    |       |        | Que Status Interrupt Register                            |                      |

|    |       |        | Rule Control Register                                    |                      |

|    |       |        | Rule Match Register                                      |                      |

|    |       |        | CAM Address Register                                     |                      |

|    |       |        | Power Management Control and Status Register             |                      |

|    |       |        | Power Management Capabilities                            |                      |

|    |       |        | Water Mark Values Register                               |                      |

|    |       |        | Wake Up Status Register                                  |                      |

|    |       |        | Host Not Responding Count Register                       |                      |

|    |       |        | Pause Delay Count Register                               |                      |

|    |       |        | Interrupt Delay Count Register                           |                      |

|    |       |        | Snoop Control Register                                   |                      |

|    |       |        | Counter Management Register                              |                      |

|    |       | 7.6.20 | Counter Control Register                                 | . 65                 |

|    |       |        | Count Data Register                                      |                      |

|    |       |        | MAC Control Register                                     |                      |

|    |       |        | PROM Control Register                                    |                      |

|    |       |        | PROM Data Register                                       |                      |

|    |       |        | Station Management Control and Address Register          |                      |

|    |       |        | Station Management Data Register                         |                      |

|    |       |        | BIST Bypass Mode Data Register                           |                      |

|    |       | 7.6.12 | BIST Control Register                                    | . 62                 |

|    |       | 7.6.11 | Receive Data Status Register                             | . 62                 |

|    |       | 7.6.10 | Receive FIRST BLOCK Status Register                      | . 61                 |

|    |       | 7.6.9  | Frame Disposition Register                               | . 61                 |

|    |       |        | Receive to Transmit Transfer Register                    |                      |

|    |       | 7.6.7  | Configuration                                            | . 61                 |

|    |       |        | Revision ID                                              |                      |

|    |       |        | Receive Producer Status                                  |                      |

|    |       |        | Transmit Producer Status                                 |                      |

|    |       | 7.6.3  | Transmit Packet Status Register                          | . 59                 |

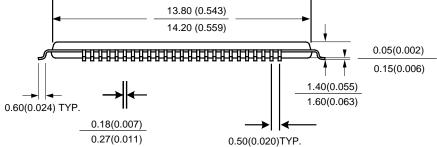

| 12   | Package Mechanical Drawing (100-pin LQFP)                                          | . 86 |

|------|------------------------------------------------------------------------------------|------|

| 13   | Ordering Information                                                               | . 87 |

| 14   | Related Documentation                                                              | . 87 |

| 15   | Contact Information                                                                |      |

| 13   | Contact information                                                                | .01  |

|      |                                                                                    |      |

| Tab  | les                                                                                |      |

|      |                                                                                    |      |

|      | e 1: Pin Legend                                                                    |      |

|      | e 2: Clock Pin Descriptions                                                        |      |

|      | e 3: MDI Pin Descriptions                                                          |      |

|      | e 4: LED Pin Descriptions                                                          |      |

|      | e 5: EEPROM Interface Pin Descriptions                                             |      |

|      | e 6: GBI Data Pin Descriptions                                                     |      |

|      | e 7: GBI Address Pin Descriptions                                                  |      |

|      | e 8: GBI Control Pin Descriptions                                                  |      |

|      | e 9: Chip Mode Pin Descriptions                                                    |      |

|      | e 10: JTAG Pin Descriptions                                                        |      |

|      | e 11: Power Pin Descriptions                                                       |      |

| Tabl | e 12: Absolute Maximum Ratings                                                     | .18  |

| Tabl | e 13: Recommended Operating Conditions                                             | .18  |

|      | e 14: DC Characteristics                                                           |      |

|      | e 15: Digital I/O Characteristics                                                  |      |

|      | e 16: MII 100Base-TX Transmit Timinge 17: MII 100Base-TX Transmitter (Informative) |      |

|      | e 18: MII 100Base-TX Transmitter (miormative)                                      |      |

|      | e 19: MII 100Base-TA Receiver Hilling                                              |      |

| Tabl | e 20: MII 10Base-T Transmitter (Informative)                                       | 20   |

| Tabl | e 21: MII 10Base-T Receive Timing                                                  | 21   |

|      | e 22: Transmit Data Buffer Example                                                 |      |

|      | e 23: Counter Summary                                                              |      |

|      | e 24: CAM Rules Associated with Unicast Filter Bytes                               |      |

| Tabl | e 25: CAM Rules Associated with Multicast Filter Bytes                             | 36   |

|      | e 26: Control Logic Actions                                                        |      |

|      | e 27: RCR Match Control                                                            |      |

|      | e 28: Ethernet Frame for Classification                                            |      |

|      | e 29: Process Destination Address Rules                                            |      |

|      | e 30: Process Source Address Rules                                                 |      |

|      | e 31: Process Length/Type, MAC Control Frames and Start IP Header Checksum Rules   |      |

|      | e 32: Process Rules for OnNow Packet                                               |      |

|      | e 33: Process Rules for Magic Packet                                               |      |

|      | e 34: PHY Register Group                                                           |      |

| Tabl | e 35: Isolation Transformers                                                       | . 83 |

| Tabl | e 36: Reference Crystal                                                            | . 83 |

| Tabl | e 37: 78Q8430 Order Numbers and Packaging Marks                                    | . 87 |

|      |                                                                                    |      |

# **Figures**

| Figure 1: 78Q8430 Block Diagram           | 7  |

|-------------------------------------------|----|

| Figure 2: Set Top Box Diagram             | 8  |

| Figure 3: Network Cameras Diagram         |    |

| Figure 4: Typical FXO VoIP Application    |    |

| Figure 5: Device Block Diagram            |    |

| Figure 6: GBI Bus Block Diagram           |    |

| Figure 7: Pinout                          |    |

| Figure 8: Host Interface Timing Diagram   |    |

| Figure 9: Host Bus Output Timing Diagram  |    |

| Figure 10: Host Bus Input Timing Diagram  |    |

| Figure 11: Bus Clock Timing               | 24 |

| Figure 12: Internal Digital Block Diagram | 25 |

| Figure 13: Internal PHY Block Diagram     |    |

| Figure 14: Classification Architecture    | 33 |

| Figure 15: System Bus Interface Schematic |    |

| Figure 16: Line Interface Schematic       |    |

| Figure 17: LQFP Drawing                   | 86 |

|                                           |    |

#### 1 Introduction

The Teridian 78Q8430 is a single chip 10Base-T/100Base-TX capable Fast Ethernet Media Access Controller (MAC) and Physical Layer (PHY) transceiver. The device is optimized for video applications, such as the Set Top Box (STB), and easily interfaces to available STB core processors, such as the STi5100, STi5516, STi5514, ARM<sup>™</sup> and Intel<sup>®</sup> based processors. The 78Q8430 is compliant with applicable IEEE-802.3 standards. MAC and PHY configuration and status registers are provided as specified by IEEE-802.3u.

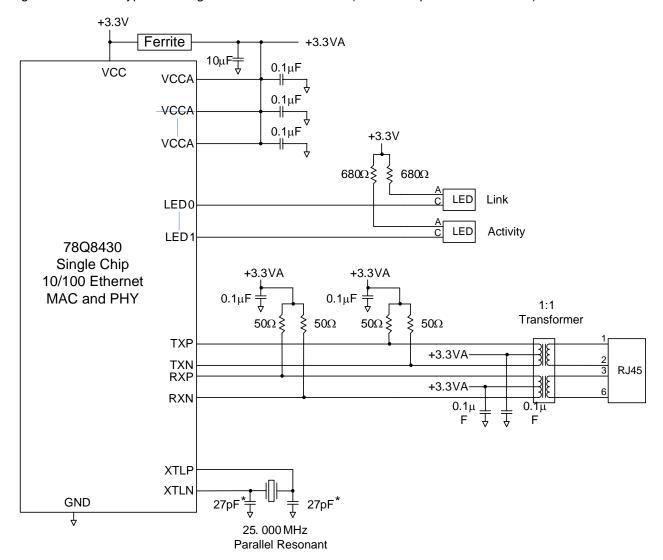

The 78Q8430 operates over Category-5 Unshielded Twisted Pair (Cat-5 UTP) cabling in 100Base-TX applications and over Cat-3 UTP in 10Base-T applications requiring only a dual 1:1 isolation transformer interface to the copper media.

The Ethernet MAC section makes use of a 32 kB deep on-chip SRAM FIFO packet memory to adaptively buffer transmit and receive data. SRAM memory can be dynamically allocated to either the transmit queues or the receive queues as required to optimize throughput.

The host processor accesses the FIFO(s) using a simple asynchronous pseudo-SRAM like host bus interface. A 32 bit wide bus is provided; the bus width can be pin-configured for 8-bit, 16-bit or 32-bit bus width at boot-up. Big endian, little endian and mixed endian options are available in 32-bit operation; little endian is available for 16-bit operation. Different End-in variations are supported through internal circuitry with minimal user intervention required.

The MAC interface logic may assert MEMWAIT during bus transactions, requesting wait states from the host while critical internal data transfer completes. The MAC provides both half duplex and full duplex operation, as well as support for full duplex flow control. Complete, portable device drivers for Linux<sup>®</sup>, OS20 and VxWorks<sup>®</sup> are available.

The 78Q8430 operates from a single 3.3 V supply. Power down modes and power saving modes are available. The 78Q8430 defaults to use an on-chip crystal oscillator. In this mode, a 25 MHz reference crystal is connected between the XTLP and XTLN pins. Alternatively, an externally generated 25 MHz clock can be connected to the XTLP pin. The chip will automatically configure itself to use the external clock. In this mode of operation, a crystal is not required.

# 1.1 Systems Applications

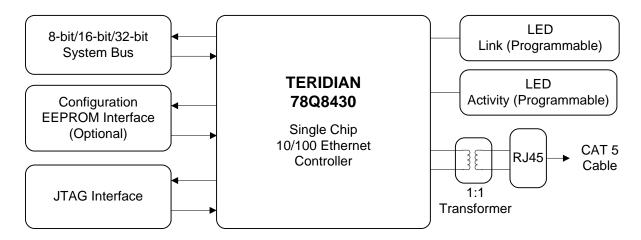

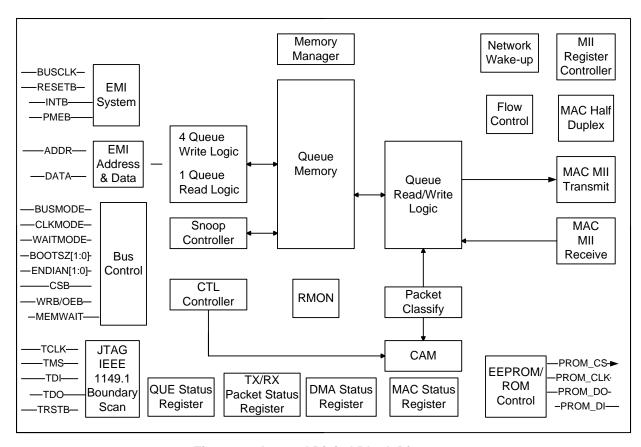

Figure 1 presents an overview of the 78Q8430 in a block diagram.

Figure 1: 78Q8430 Block Diagram

# 1.2 System Level Application Information

This section provides an overview of system level applications in some typical high-volume consumer equipment.

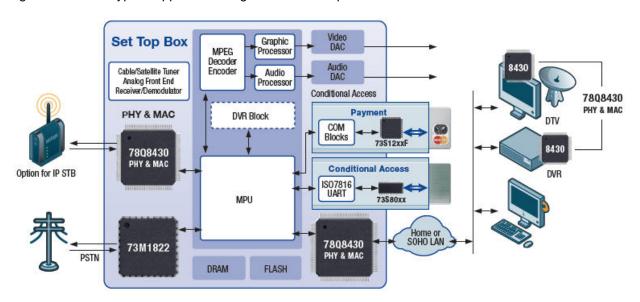

# 1.2.1 Set Top Box Application

Figure 2 shows a typical application diagram for a set top box.

Figure 2: Set Top Box Diagram

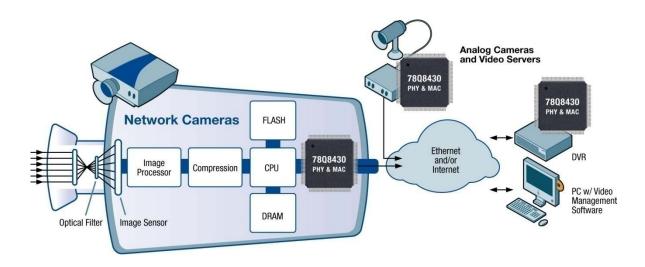

### 1.2.2 IP Security Application

Figure 3 shows a typical application diagram for an IPTV security camera application.

Figure 3: Network Cameras Diagram

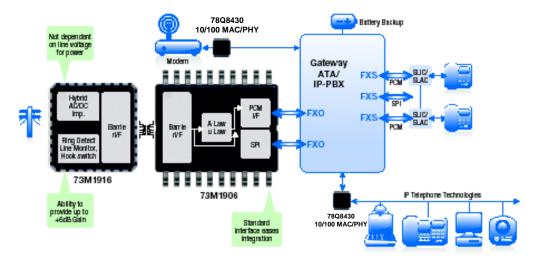

### 1.2.3 IP PBX Application

Figure 4 shows a typical application diagram for an IP PBX application.

Figure 4: Typical FXO VoIP Application

#### 1.3 Overview

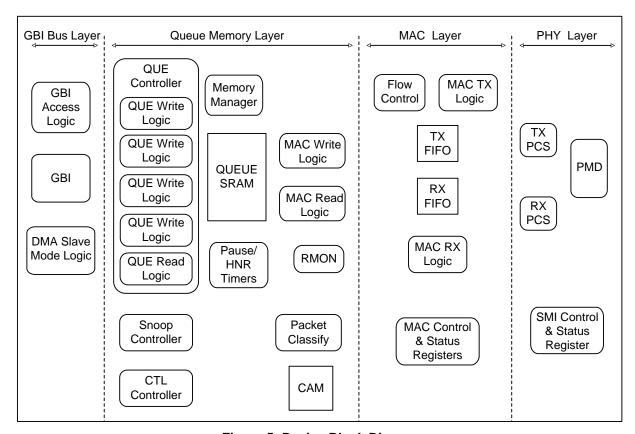

The 78Q8430 is divided into four sections, as shown in Figure 5.

- Generic Bus Interface (GBI) Control Layer

- Queue Memory Layer

- Ethernet Media Access Control (MAC) Layer

- Ethernet Physical (PHY) Layer

Figure 5: Device Block Diagram

# 1.4 Application Environments

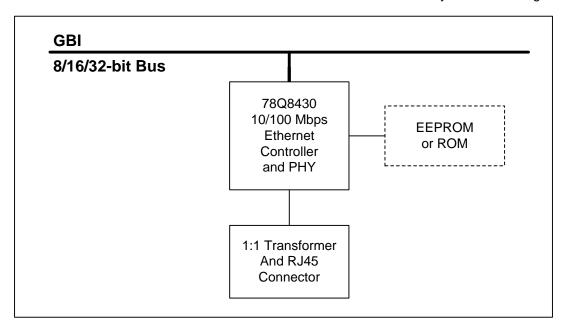

This section provides an overview of the application environments such as the STMicroelectronics and Embest ARM9<sup>™</sup> processors, for which the 78Q8430 provides a seamless interface. Figure 6 shows a simple application diagram for a design using the GBI based 10/100-Mbps Ethernet Controller. By providing a direct connection to the GBI bus, applications requiring Ethernet network access can be realized with a high degree of integration. The figure shows the processor and the Ethernet controller with connected address and data buses. This connection can be either on the motherboard, or via an expansion module. The GBI Controller controls the address and data and the system control signals.

Figure 6: GBI Bus Block Diagram

Figure 6 shows the components that are likely to be used with the 10/100-Mbps Ethernet Controller. The integrated PHY is designed to directly connect to an integrated 1:1 transformer and RJ-45 connector, thereby providing a minimum parts solution.

### 1.5 Supply Voltages

The 78Q8430 requires a single 3.3 V (+/-5%) supply voltage. No external components are required to generate on-chip bias voltages and currents. High accuracy is maintained through a closed-loop trimmed biasing network. On-chip power converters generate 1.8 V power for core digital logic and memory blocks. The voltage regulator is not affected by the power-down mode.

### 1.6 Power Management

The 78Q8430 supports both normal and power-saving modes. When the GBI bus is active, it can be in normal mode or Power Management low-power modes.

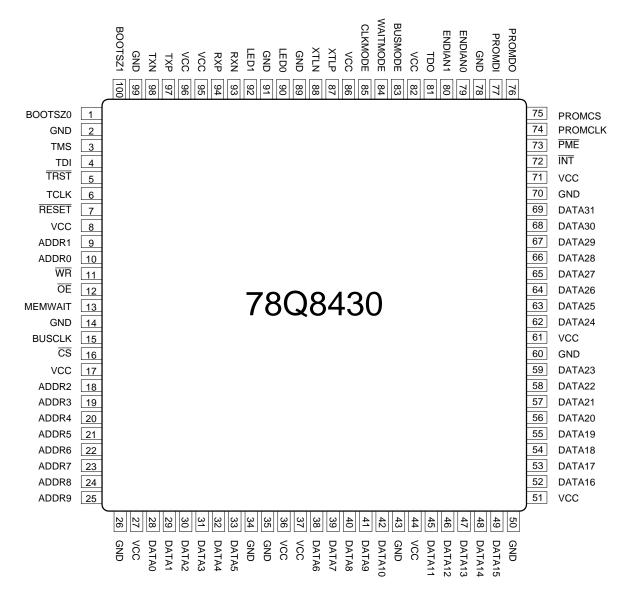

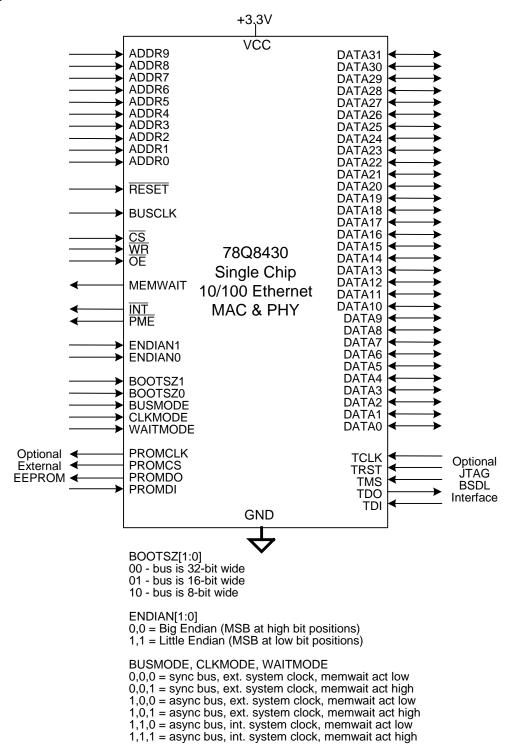

### 2 Pinout

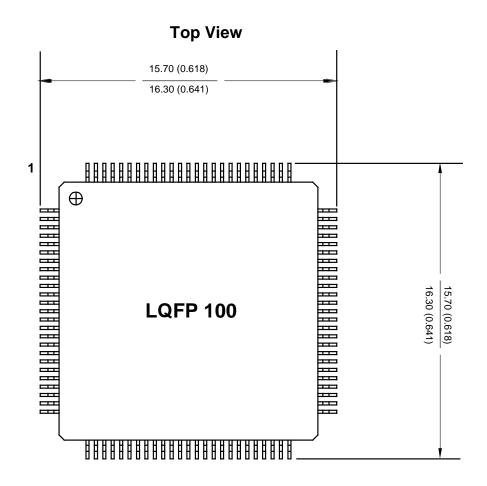

The 78Q8430 is available in a 14x14 mm 100-pin LQFP package.

Figure 7: Pinout

# 3 Pin Description

# 3.1 Pin Legend

Table 1 lists the different pin types found on the 78Q8430 device. The Type field of the pin description tables refers to one of these types.

Table 1: Pin Legend

| Туре | Description                           |

|------|---------------------------------------|

| Α    | Analog                                |

| IU   | TTL-level Input, with Pull-up         |

| IS   | TTL-level Input, with Schmitt Trigger |

| 0    | TTL-level Output                      |

| OD   | TTL-level Output (Open Drain)         |

| S    | Supply                                |

| I    | TTL-level Input                       |

| ID   | TTL-level Input, with Pull-down       |

| В    | TTL-level Bidirectional Pin           |

| OZ   | TTL-level Output (Tristate)           |

| G    | Ground                                |

# 3.2 Pin Descriptions

The pin descriptions in the following tables are grouped by interface. A pin number, type specification per Table 2 and a functional description is provided for each pin on the 78Q8430 device.

#### 3.2.1 Clock Pins

**Table 2: Clock Pin Descriptions**

| Signal | Pin Number | Туре | Description                                                                                                                                                                                                                                                                                                                                                   |

|--------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTLP   | 87         | Α    | Crystal Positive/Negative                                                                                                                                                                                                                                                                                                                                     |

| XTLN   | 88         |      | To use the internal oscillator, connect a 25 MHz crystal across XTLP and XTLN. To use of an external clock, XTLN is grounded and XTLP is driven with a 25 MHz clock.  Provides timing reference for all media dependant interface operations. An internal PLL is used to multiply this clock by four for use as the main system clock in internal clock mode. |

| BUSCLK | 15         | I    | Peripheral Clock The source for the main system clock in external clock mode. In synchronous bus mode, all host bus signals are assumed to be synchronous to this clock.                                                                                                                                                                                      |

# 3.2.2 Media Dependent Interface (MDI) Pins

**Table 3: MDI Pin Descriptions**

| Signal | Pin Number | Туре | Description                                                                                                                                             |

|--------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXP    | 97         | Α    | Transmit Output Positive/Negative                                                                                                                       |

| TXN    | 98         | Α    | Transmitter outputs for both 10BASE-T and 100BASE-TX.  MDI-X Mode: Receive Input Positive/Negative Receiver inputs for both 10BASE-T and 100BASE-TX.    |

| RXP    | 94         | Α    | Receive Input Positive/Negative                                                                                                                         |

| RXN    | 93         | A    | Receiver inputs for both 10BASE-T and 100BASE-TX.  MDI-X Mode: Transmit Output Positive/Negative  Transmitter outputs for both 10BASE-T and 100BASE-TX. |

# 3.2.3 LED Display (PHY) Pins

The LED pins use standard logic drivers. They output a logic low when the LED is meant to be on and are tri-state when it is meant to be off. The LED cathode should be connected to the output pin and a series resistor from the power supply connected to the LED anode.

**Table 4: LED Pin Descriptions**

| Signal | Pin Number | Type | Description                                                                       |

|--------|------------|------|-----------------------------------------------------------------------------------|

| LED0   | 90         | OZ   | PHY display LED0 (Link OK)                                                        |

|        |            |      | The default for LED0 is Link OK (LED is on for link established).                 |

| LED1   | 92         | OZ   | PHY display LED1 (Activity)                                                       |

|        |            |      | The default for LED1 is Link Activity (LED blinks for Rx or Tx data transferred). |

### 3.2.4 EEPROM Pins

**Table 5: EEPROM Interface Pin Descriptions**

| Signal   | Pin Number | Туре | Description                                                                                                                                                  |

|----------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROM_CS  | 75         | 0    | EEPROM Chip Select                                                                                                                                           |

|          |            |      | Used to frame transmissions to and from an external EEPROM.                                                                                                  |

| PROM_CLK | 74         | 0    | EEPROM Clock                                                                                                                                                 |

|          |            |      | Clock for transmitting to and from an external EEPROM/ROM. This is compatible with the slowest commercial parts, which specify a maximum frequency of 1 MHz. |

| PROM_DI  | 77         | I    | EEPROM Data In  Data line for transmitting from the external EEPROM to the controller. Must be high with no EEPROM present.                                  |

| PROM_DO  | 76         | OZ   | EEPROM Data Out Transfers data from the controller to an external EEPROM/ROM.                                                                                |

# 3.2.5 GBI Data Pins

**Table 6: GBI Data Pin Descriptions**

| Signal | Pin Number | Туре | Description                                                                                                           |

|--------|------------|------|-----------------------------------------------------------------------------------------------------------------------|

| DATA31 | 69         | В    | Data Bus DATA[31:0]                                                                                                   |

| DATA30 | 68         |      | Bi-directional host bus data. The BOOTSZ pins determine how                                                           |

| DATA29 | 67         |      | many of these are actually used. The $\overline{OE}$ input will disable the output drivers to prevent bus collisions. |

| DATA28 | 66         |      | output univers to prevent bus comsions.                                                                               |

| DATA27 | 65         |      |                                                                                                                       |

| DATA26 | 64         |      |                                                                                                                       |

| DATA25 | 63         |      |                                                                                                                       |

| DATA24 | 62         |      |                                                                                                                       |

| DATA23 | 59         |      |                                                                                                                       |

| DATA22 | 58         |      |                                                                                                                       |

| DATA21 | 57         |      |                                                                                                                       |

| DATA20 | 56         |      |                                                                                                                       |

| DATA19 | 55         |      |                                                                                                                       |

| DATA18 | 54         |      |                                                                                                                       |

| DATA17 | 53         |      |                                                                                                                       |

| DATA16 | 52         |      |                                                                                                                       |

| DATA15 | 49         |      |                                                                                                                       |

| DATA14 | 48         |      |                                                                                                                       |

| DATA13 | 47         |      |                                                                                                                       |

| DATA12 | 46         |      |                                                                                                                       |

| DATA11 | 45         |      |                                                                                                                       |

| DATA10 | 42         |      |                                                                                                                       |

| DATA9  | 41         |      |                                                                                                                       |

| DATA8  | 40         |      |                                                                                                                       |

| DATA7  | 39         |      |                                                                                                                       |

| DATA6  | 38         |      |                                                                                                                       |

| DATA5  | 33         |      |                                                                                                                       |

| DATA4  | 32         |      |                                                                                                                       |

| DATA3  | 31         |      |                                                                                                                       |

| DATA2  | 30         |      |                                                                                                                       |

| DATA1  | 29         |      |                                                                                                                       |

| DATA0  | 28         |      |                                                                                                                       |

# 3.2.6 GBI Address Pins

**Table 7: GBI Address Pin Descriptions**

| Signal | Pin Number | Туре | Description                                                                                                                                                                                                                                                                                                    |

|--------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR9  | 25         | I    | Address Bus                                                                                                                                                                                                                                                                                                    |

| ADDR8  | 24         | I    | The address lines are required to be stable for the entire duration                                                                                                                                                                                                                                            |

| ADDR7  | 23         | I    | of a $\overline{CS}$ cycle. In synchronous bus mode, the address pins are sampled on the first rising edge of BUSCLK that $\overline{CS}$ is asserted low. In asynchronous bus mode, the address pins are sampled as soon as the falling edge of $\overline{CS}$ is synchronized to the internal system clock. |

| ADDR6  | 22         | I    |                                                                                                                                                                                                                                                                                                                |

| ADDR5  | 21         | -    |                                                                                                                                                                                                                                                                                                                |

| ADDR4  | 20         | -    |                                                                                                                                                                                                                                                                                                                |

| ADDR3  | 19         | -    | In 22 hit hus made, ADDRIA:01 are ignored. In 16 hit hus made                                                                                                                                                                                                                                                  |

| ADDR2  | 18         | -    | In 32-bit bus mode, ADDR[1:0] are ignored. In 16-bit bus mode, ADDR[0] is ignored. In 8-bit bus mode, all ADDR bits are used to                                                                                                                                                                                |

| ADDR1  | 9          | I    | reference a register byte.                                                                                                                                                                                                                                                                                     |

| ADDR0  | 10         | I    | -                                                                                                                                                                                                                                                                                                              |

# 3.2.7 GBI Control Pins

**Table 8: GBI Control Pin Descriptions**

| Signal  | Pin Number | Туре | Description                                                                                                                                                                                                                                                                                           |

|---------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET   | 7          | I    | Reset (active low) Referred to as hardware reset. Causes all 78Q8430 outputs to enter a high-impedance state, stops all current operations and initializes registers.                                                                                                                                 |

| CS      | 16         | I    | Chip Select (active low) The Processor asserts this signal to initiate a read or write operation.                                                                                                                                                                                                     |

| WR      | 11         | I    | Write Enable (active low) The Processor asserts WR to indicate a write operation.                                                                                                                                                                                                                     |

| OE      | 12         | I    | Output Enable (active low) The Processor asserts OE to enable the 78Q8430 data drivers during a read cycle.                                                                                                                                                                                           |

| MEMWAIT | 13         | OZ   | Memory Wait  During a bus cycle the 78Q8430 asserts MEMWAIT to indicate that it is not ready to drive or receive valid data on the DATA lines. The polarity is dependent on the WAITMODE pin. When WAITMODE is high then the pin is asserted high; when WAITMODE is low then the pin is asserted low. |

| ĪNT     | 72         | OD   | Interrupt (active low) The 78Q8430 asserts the INT signal low when it detects an interrupt event.                                                                                                                                                                                                     |

| PME     | 73         | OD   | Power Management Event (active low) The 78Q8430 asserts the PME signal low when it detects a wake-up event.                                                                                                                                                                                           |

### 3.2.8 Mode Pins

**Table 9: Chip Mode Pin Descriptions**

| Signal   | Pin Number | Type | Description                                                                                                                                                                                                                                                                                                       |

|----------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUSMODE  | 83         | I    | BUSMODE, CLKMODE, WAITMODE Configuration                                                                                                                                                                                                                                                                          |

| CLKMODE  | 85         | I    | 0,0,0 = Sync bus, ext. system clock, memwait act low                                                                                                                                                                                                                                                              |

| WAITMODE | 84         | I    | 0,0,1 = Sync bus, ext. system clock, memwait act high 0,1,0 = Reserved 0,1,1 = Reserved 1,0,0 = Async bus, ext. system clock, memwait act low 1,0,1 = Async bus, ext. system clock, memwait act high 1,1,0 = Async bus, int. system clock, memwait act low 1,1,1 = Async bus, int. system clock, memwait act high |

| ENDIAN0  | 79         | I    | Data Bus Endian Select                                                                                                                                                                                                                                                                                            |

| ENDIAN1  | 80         | I    | 0,0 = Big endian (MSB at high bit positions) 0,1 = Bytes are little endian inside 16-bit words 1,0 = Word endian (MSW at low bit positions) 1,1 = Little endian (MSB at low bit positions)                                                                                                                        |

| BOOTSZ1  | 100        | I    | GBI Bus Size                                                                                                                                                                                                                                                                                                      |

| BOOTSZ0  | 1          | I    | BOOTSZ[1:0]: is strapped to indicate the GBI bus size:  00 = Bus is 32 bits wide  01 = Bus is 16 bits wide. Only DATA[15:0] are used.  10 = Bus is 8 bits wide. Only DATA[7:0] are used.  11 = Reserved                                                                                                           |

### Notes:

- 1. The internal PHY should never be powered down when the internal system clock is selected by the CLKMODE pin (CLKMODE=1)

- 2. There is no external visibility for the system clock when the internal clock mode is selected. The GBI interface must therefore always be used in asynchronous bus mode.

#### 3.2.9 JTAG Pins

**Table 10: JTAG Pin Descriptions**

| Signal | Pin Number | Туре | Description                                                      |

|--------|------------|------|------------------------------------------------------------------|

| TRST   | 5          | I    | Test Reset (active low)                                          |

|        |            |      | System provided reset for JTAG logic.                            |

| TCLK   | 6          | ı    | Test Clock                                                       |

|        |            |      | System provided clock for JTAG logic.                            |

| TMS    | 3          | IU   | Test Mode Select                                                 |

|        |            |      | Enables JTAG boundary scan using serial in/serial out ports.     |

|        |            |      | Sampled on rising edge of TCLK.                                  |

| TDI    | 4          | IU   | Test Data In                                                     |

|        |            |      | Serial input port for clocking in test data to be shifted to the |

|        |            |      | output at the end of the boundary scan chain (TDO).              |

| TDO    | 81         | 0    | Test Data Out                                                    |

|        |            |      | Serial output port for clocking out test data shifted from the   |

|        |            |      | input at the beginning of the boundary scan chain (TDI).         |

# 3.2.10 Power Pins

**Table 11: Power Pin Descriptions**

| Signal | Pin Number | Type | Description                                   |

|--------|------------|------|-----------------------------------------------|

| VCCA   | 86         | S    | 3.3 V supply for the analog transmit section. |

|        | 95         |      |                                               |

|        | 96         |      |                                               |

| VCC    | 8          | S    | 3.3 V supply for the digital logic section.   |

|        | 17         |      |                                               |

|        | 27         |      |                                               |

|        | 36-37      |      |                                               |

|        | 44         |      |                                               |

|        | 51         |      |                                               |

|        | 61         |      |                                               |

|        | 71         |      |                                               |

|        | 82         |      |                                               |

| GND    | 2          | G    | Common ground return.                         |

|        | 14         |      |                                               |

|        | 26         |      |                                               |

|        | 34-35      |      |                                               |

|        | 43         |      |                                               |

|        | 50         |      |                                               |

|        | 60         |      |                                               |

|        | 70         |      |                                               |

|        | 78         |      |                                               |

|        | 89         |      |                                               |

|        | 91         |      |                                               |

|        | 99         |      |                                               |

# 4 Electrical Specification

# 4.1 Absolute Maximum Ratings

Operation above the maximum rating may permanently damage the device.

**Table 12: Absolute Maximum Ratings**

| Parameter                              | Rating                             |

|----------------------------------------|------------------------------------|

| DC Supply Voltage (V <sub>CC</sub> )   | -0.5 to 4.0 VDC                    |

| Storage Temperature                    | -65 to 150 °C                      |

| Pin Voltage (except TXOP/N and RXIP/N) | -0.3 to (V <sub>CC</sub> +0.6) VDC |

| Pin Voltage (TXOP/N and RXIP/N only)   | -0.3 to (V <sub>CC</sub> +1.4) VDC |

| Pin Current                            | ± 120 mA                           |

# 4.2 Recommended Operation Conditions

Unless otherwise noted all specifications are valid over these temperatures and supply voltage ranges.

**Table 13: Recommended Operating Conditions**

| Parameter                                         | Rating         |

|---------------------------------------------------|----------------|

| DC Voltage Supply (V <sub>CC</sub> )              | 3.3 ± 0.17 VDC |

| Ambient Operating Temperature (T <sub>AMB</sub> ) | -40 to +85 °C  |

### 4.3 DC Characteristics

**Table 14: DC Characteristics**

| Parameter      | Symbol          | Conditions                                                                                     | Min | Nom                           | Max                           | Unit    |

|----------------|-----------------|------------------------------------------------------------------------------------------------|-----|-------------------------------|-------------------------------|---------|

| Supply Current | I <sub>CC</sub> | V <sub>CC</sub> = 3.3 V<br>Auto-Negotiation<br>10BT (Idle)<br>10BT (Normal Activity)<br>100BTX | -   | -<br>124<br>110<br>230<br>165 | -<br>150<br>140<br>250<br>190 | –<br>mA |

| Supply Current | I <sub>CC</sub> | Power-down mode                                                                                | _   | 14                            | 45                            | mA      |

# 4.4 Digital I/O Characteristics

Table 15: Digital I/O Characteristics

| Parameter                            | Symbol                            | Conditions                                                 | Min | Nom | Max | Unit |

|--------------------------------------|-----------------------------------|------------------------------------------------------------|-----|-----|-----|------|

| Input Voltage Low                    | V <sub>IL</sub>                   |                                                            | -   | _   | 0.8 | V    |

| Input Voltage High                   | V <sub>IH</sub>                   |                                                            | 2.0 | _   | -   | V    |

| Input Current                        | I <sub>IL</sub> , I <sub>IH</sub> |                                                            | -1  | _   | 1   | μΑ   |

| Input Capacitance                    | C <sub>IN</sub>                   |                                                            | _   | 8   | _   | pF   |

| Output Voltage Low                   | V <sub>OL</sub>                   | $I_{OL} = 8 \text{ mA}$                                    | _   | _   | 0.4 | V    |

| Output Voltage<br>High**             | V <sub>OH</sub>                   | I <sub>OH</sub> = -8 mA                                    | 2.4 | _   | _   | V    |

| Output Transition<br>Time            | T <sub>T</sub>                    | $C_L = 20 \text{ pF}$<br>$I_{OH} = -8 \text{ ma (H to Z)}$ | _   | _   | 6   | ns   |

| Tri-state Output<br>Leakage Current* | I <sub>Z</sub>                    | Type tri-state only                                        | -1  | _   | 1   | μΑ   |

<sup>\*\*</sup>PMEB and INTB are active low outputs requiring external pull-up resistors. V<sub>OH</sub> for these outputs is not specified.

# 4.5 Analog Electrical Characteristics

# 4.5.1 100Base-TX Transmitter

Table 16: MII 100Base-TX Transmit Timing

| Parameter                                                                       | Conditions                                             | Min  | Nom | Max  | Unit |

|---------------------------------------------------------------------------------|--------------------------------------------------------|------|-----|------|------|

| Peak Output Amplitude ( V <sub>P</sub> + ,  V <sub>P</sub> - ) (see note below) | Best-fit over 14 bit times;<br>0.4 dB Transformer loss | 950  | _   | 1050 | mVpk |

| Output Amplitude Symmetry                                                       | V <sub>P</sub> + <br> V <sub>P</sub> -                 | 0.98 | -   | 1.02 |      |

| Output Overshoot                                                                | Percent of V <sub>P</sub> +, V <sub>P</sub> -          | _    | _   | 5    | %    |

| Rise/Fall time (t <sub>R</sub> , t <sub>F</sub> )                               | 10-90% of V <sub>P</sub> +, V <sub>P</sub> -           | 3    | _   | 5    | ns   |

| Rise/Fall time Imbalance                                                        | $ t_R - t_F $                                          | _    | _   | 500  | ps   |

| Duty Cycle Distortion                                                           | Deviation from best-fit time-grid; 010101 Sequence     | _    | -   | ±250 | ps   |

| Jitter                                                                          | Scrambled Idle, Internal Oscillator Mode               | _    | _   | 1.4  | ns   |

Note: Measured at the line side of the transformer. Test Condition: Transformer P/N: TLA-6T103. Line Termination: 100  $\Omega$ ±1%

# 4.5.2 100Base-TX Transmitter (Informative)

**Table 17: MII 100Base-TX Transmitter (Informative)**

| Parameter               | Conditions                  | Min                                       | Max | Unit |

|-------------------------|-----------------------------|-------------------------------------------|-----|------|

| Return Loss             | 2 < f < 30 MHz              | 16                                        | _   | dB   |

|                         | 30 < f < 60 MHz             | $16 - 20\log\left(\frac{f}{30MHz}\right)$ |     |      |

|                         | 60 < f < 80 MHz             | 10                                        |     |      |

| Open-Circuit Inductance | -8 < I <sub>IN</sub> < 8 mA | 350                                       | ı   | μΗ   |

Note: The specifications in the preceding table are included for information only. They are mainly a function of the external transformer and termination resistors used for measurements.

#### 4.5.3 100Base-TX Receiver

Table 18: MII 100Base-TX Receiver Timing

| Parameter                            | Conditions | Min | Nom | Max  | Unit  |

|--------------------------------------|------------|-----|-----|------|-------|

| Signal Detect Assertion Threshold    |            | 600 | 700 | 800  | mVppd |

| Signal Detect De-assertion Threshold |            | 300 | 350 | 400  | mVppd |

| Differential Input Resistance        |            | _   | 20  | _    | kΩ    |

| Jitter Tolerance (pk-pk)             |            | 4   | -   | -    | ns    |

| Baseline Wander Tracking             |            | -75 | _   | +75  | %     |

| Signal Detect Assertion Time         | Not tested | _   | -   | 1000 | μS    |

| Signal Detect De-assertion Time      | Not tested | _   | _   | 4    | μS    |

#### 4.5.4 10Base-T Transmitter

Table 19: MII 10Base-T Transmitter Timing

| Parameter                                        | Conditions                            | Min | Nom | Max | Unit |

|--------------------------------------------------|---------------------------------------|-----|-----|-----|------|

| Peak Differential Output Signal (see note below) | All data patterns                     | 2.2 | 1   | 2.8 | V    |

| Harmonic Content (dB below fundamental)          | Any harmonic All ones data Not tested | 27  | -   | I   | dB   |

| Link Pulse Width                                 |                                       | _   | 100 | -   | ns   |

| Start-of-Idle Pulse Width                        | Last bit 0                            | _   | 300 | _   | ns   |

|                                                  | Last bit 1                            | _   | 350 | _   | ns   |

Note: The Manchester-encoded data pulses, the link pulse and the start-of-idle pulse are tested against the templates and using the procedures found in Clause 14 of IEEE 802.3. Measured at the line side of the transformer. Test Condition: Transformer P/N: TLA-6T103. Line Termination:  $100 \Omega \pm 1\%$

## 4.5.5 10Base-T Transmitter (Informative)

Table 20: MII 10Base-T Transmitter (Informative)

| Parameter                       | Conditions                                                                                      | Min                                      | Nom | Max | Unit |

|---------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------|-----|-----|------|

| Output Return Loss              |                                                                                                 | 15                                       | _   | _   | dB   |

| Output Impedance Balance        | 1 MHz < freq < 20 MHz                                                                           | $29 - 17 \log \left(\frac{f}{10}\right)$ | 1   | _   | dB   |

| Peak Common-mode Output Voltage |                                                                                                 | _                                        | -   | 50  | mV   |

| Common-mode Rejection           | 15 V <sub>PK</sub> , 10.1 MHz sine wave applied to transmitter common-mode. All data sequences. | _                                        | _   | 100 | mV   |

| Common-mode Rejection Jitter    | 15 V <sub>PK</sub> , 10.1 MHz sine wave applied to transmitter common-mode. All data sequences. | _                                        | _   | 1   | ns   |

Note: The specifications in the preceding table are included for information only. They are mainly a function of the external transformer and termination resistors used for measurements

# 4.5.6 10Base-T Receiver

Table 21: MII 10Base-T Receive Timing

| Parameter                     | Conditions                                   | Min | Nom               | Max | Unit  |

|-------------------------------|----------------------------------------------|-----|-------------------|-----|-------|

| DLL Phase Acquisition Time    |                                              | _   | 10                | _   | BT    |

| Jitter Tolerance (pk-pk)      |                                              | 30  | -                 | _   | ns    |

| Input Squelched Threshold     |                                              | 500 | 600               | 700 | mVppd |

| Input Unsquelched Threshold   |                                              | 275 | 350               | 425 | mVppd |

| Differential Input Resistance |                                              | _   | 20                | _   | kΩ    |

| Bit Error Ratio               |                                              | _   | 10 <sup>-10</sup> | _   |       |

| Common-mode Rejection         | Square wave<br>0 < f < 500 kHz<br>Not tested | 25  | _                 | _   | V     |

# 5 Host Interface Timing Specification

# 5.1 Host Interface

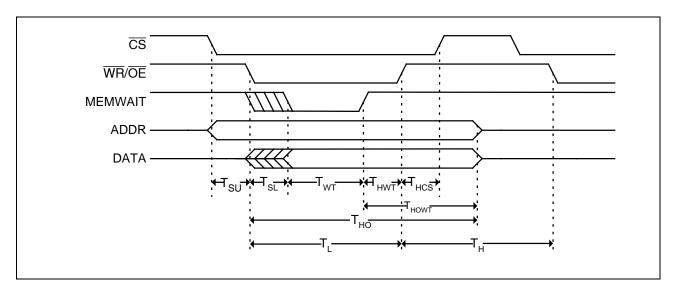

Figure 8: Host Interface Timing Diagram

| Name             | Description             | Requirement                                                                                                                                           | Min    | Max     |

|------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|

| T <sub>SU</sub>  | CS and ADDR setup time  | CS and ADDR must be stable on or before the falling edge of WR/OE.                                                                                    | 0 ns   | 1       |

| T <sub>SL</sub>  | Output settling time    | The maximum amount of time that it will take the MEMWAIT, or DATA when there is no MEMWAIT, outputs to become stable after the falling edge of WR/OE. | _      | 13.7 ns |

| T <sub>WT</sub>  | Maximum wait time       | The maximum amount of time that the MEMWAIT output will held asserted.                                                                                | 1      | 17 ck   |

| T <sub>HWT</sub> | Wait hold time          | The minimum amount of time that the WR/OE input must be held past the de-assertion of MEMWAIT.                                                        | 10 ns  | ı       |

| T <sub>HCS</sub> | CS hold time            | The $\overline{\text{CS}}$ input must be stable low for the entire duration of the $\overline{\text{WR}}/\overline{\text{OE}}$ low cycle.             | 0 ns   | ı       |

| T <sub>HO</sub>  | ADDR and DATA hold time | The ADDR and DATA inputs must be stable for no less than this amount of time after the falling edge of WR.                                            | 2.5 ck | -       |

| T <sub>L</sub>   | WR/OE min low pulse     | The minimum amount of time that the WR/OE inputs must be held low.                                                                                    | 2 ck   | -       |

| T <sub>H</sub>   | WR/OE min high pulse    | The minimum amount of time that the WR/OE inputs must be held high.                                                                                   | 2 ck   | _       |

**Note:** On read cycles when MEMWAIT is asserted the DATA outputs will be valid before the de-assertion of MEMWAIT.

# 5.1.1 Synchronous Mode Timing

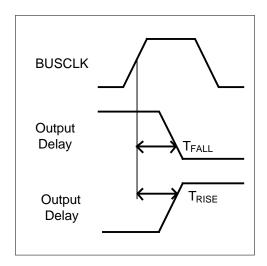

Figure 9: Host Bus Output Timing Diagram

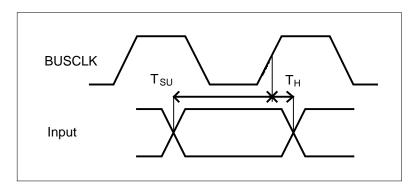

**Figure 10: Host Bus Input Timing Diagram**

| Parameter         | Symbol          | Min | Nom | Max | Unit |

|-------------------|-----------------|-----|-----|-----|------|

| Input Setup Time  | T <sub>SU</sub> | 6   | _   | _   | ns   |

| Input Hold Time   | T <sub>H</sub>  | 6   | -   | -   | ns   |

| Output Fall Delay | $T_{FALL}$      | _   | _   | 8   | ns   |

| Output Rise Delay | $T_{RISE}$      | _   | _   | 8   | ns   |

| CSB min low       | $P_{WL}$        | 1   | -   | -   | clk  |

| CSB min high      | P <sub>WH</sub> | 2   | -   | -   | clk  |

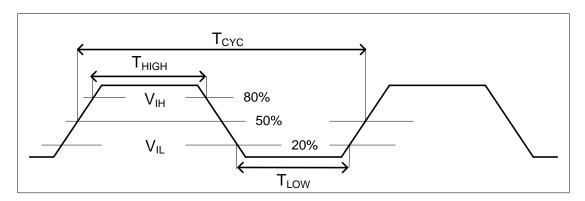

# 5.1.2 Bus Clock Timing

Figure 11: Bus Clock Timing

| Donomotor         | Cumb al           | Sync 50 |     | Async 100 |     | Unito |  |

|-------------------|-------------------|---------|-----|-----------|-----|-------|--|

| Parameter         | Symbol            | Min     | Max | Min       | Max | Units |  |

| BUSCLK Cycle Time | T <sub>CYC</sub>  | 20      | _   | 10        | _   | ns    |  |

| BUSCLK Frequency  | _                 | _       | 50  | _         | 100 | MHz   |  |

| BUSCLK High Time  | T <sub>HIGH</sub> | 8       | _   | 3         | _   | ns    |  |

| BUSCLK Low Time   | $T_{LOW}$         | 8       | _   | 3         | _   | ns    |  |

| BUSCLK Slew Rate  | _                 | 1       | 3   | 1         | 3   | V/ns  |  |

# 5.1.3 Reset Timing

| Parameter               | Symbol             | Min | Nom | Max | Units  |

|-------------------------|--------------------|-----|-----|-----|--------|

| RESETB Minimum Duration | T <sub>RESET</sub> | 1   | _   | _   | clocks |

# 6 Functional Description

# 6.1 Internal Block Diagrams

#### 6.1.1 Internal Digital Block

Figure 12 presents an overview of the functional layers of the 78Q8430. On the left side are the signals, which connect to the GBI bus. On the upper and middle right, the blocks that implement the MAC side of the MII are shown. These blocks are connected to the embedded PHY. On the lower right, connections to the EEPROM are shown.

Figure 12: Internal Digital Block Diagram

#### 6.1.2 Internal PHY

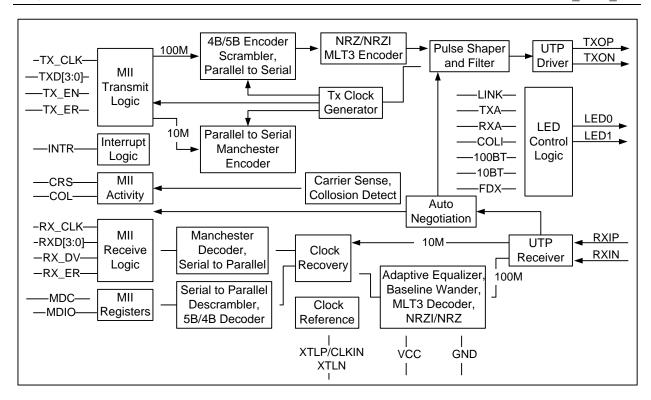

Figure 13 shows the functional blocks of the internal 78Q8430 PHY. The signals shown on the left side are the internal MII signals to the MAC. These signals are multiplexed with their respective external pins for use with an external PHY device. The 78Q8430 is not a two-port device. Only one PHY interface can be operational.

Figure 13: Internal PHY Block Diagram

On the right side are the signals, which connect to the status LEDs and a 1:1 isolation transformer before connecting to an RJ-45 connector, or equivalent media components.

# 6.2 Data Queuing

Ethernet frame data in the 78Q8430 is managed in queuing structures called QUEs. The host bus address space allocated for QUEs has enough space for eight, while the 78Q8430 circuit only implements five. QUEs are identified numerically, QUE0 through QUE7, based on the registers in the QUE register space that are used to access them. QUE1, QUE6 and QUE7 are unimplemented and reserved for future use.

A QUE allocates main buffer memory as needed and stores discrete frames as they are written into the QUE. The QUE then reads back frames in the same order that they were written and frees the main buffer memory. A QUE can contain a maximum of 125 frames at any one time. If a QUE is unable to allocate main buffer memory when writing a frame, the frame will be partially added to the QUE as a truncated frame. If a QUE is unable to allocate main buffer memory to start a frame, the entire frame is dropped.

The QUEs are divided into two categories: receive QUEs, that store received frame data and transmit QUEs, that store transmit frame data. Frames are written to a receive QUE by the MAC and read out by the host. Frames are written to a transmit QUE by the host and read out by the MAC. QUE0 and QUE1 are receive QUEs (only QUE0 is implemented), and QUE2 through QUE7 are transmit QUEs (QUE2 through QUE5 are implemented). Writing to the *Transmit Data Register* (TDR) for a receive QUE or reading from the *Read Data Register* (RDR) for a transmit QUE is not supported and the result is undefined in this specification.

The transmit QUEs are further divided into standard QUEs, as described above, and static QUEs. Static QUEs differ from the standard QUEs in that they can only contain a single frame, and that frame must be 252 bytes or less in total size. Unlike standard QUEs, static QUEs do not remove a frame when it is read from the QUE. Once a frame is written to a static QUE, it can be read out any number of times and the static QUE will always read out the same one frame. If a second frame is written to a static QUE then it will replace the first as the one frame contained in the QUE.

The purpose of a static transmit QUE is to allow the host to configure a frame that will need to be transmitted multiple times or transmitted at a later time without any interaction with the host. Transmit QUE2 and QUE5 are static QUEs. Transmit QUE2 is best suited for MAC control pause frames as it can be triggered to transmit by a main buffer watermark. Transmit QUE5 is best suited to *Host Not Responding* (HNR) frames as it can be triggered to transmit by a host interrupt timeout.

When the MAC transmitter is idle and ready to transmit a frame, it determines which QUE to read from on a priority basis. The lowest numbered QUE containing data that needs to be transmitted is selected by the MAC, which means when more than one transmit QUE is ready, the one with the lowest number always gets priority.

#### 6.3 Host Interface

#### 6.3.1 Reading Receive Data

The status of the frame at the top of the receive FIFO can be obtained by reading the *Receive Packet Status Register* (RPSR). The 16 LSBs of the RPSR contain a count of the total number of bytes that have entered the receive FIFO for this frame. A value of zero means that there are no new frames in the receive FIFO. As frame bytes enter the FIFO, the count value is incremented. However, the count value does not decrease the bytes read out of the read FIFO such that the final value will always be the final frame size.

The MSB of the RPSR is the DONE bit. Once the last byte in the frame has entered the receive FIFO, the DONE bit is set indicating that the count value contained in the total bytes field now contains the final size in bytes of the frame and the error status and classification fields now contain the final frame status. When the DONE bit is asserted, this also indicates that the status for this frame has been removed from the receive status FIFO and future reads of the RPSR will refer to the next frame in the receive FIFO, even if all of the data for the current frame has not been retrieved.