SC28L92 View Datasheet(PDF) - NXP Semiconductors.

Part Name

Description

MFG CO.

SC28L92 Datasheet PDF : 73 Pages

| |||

NXP Semiconductors

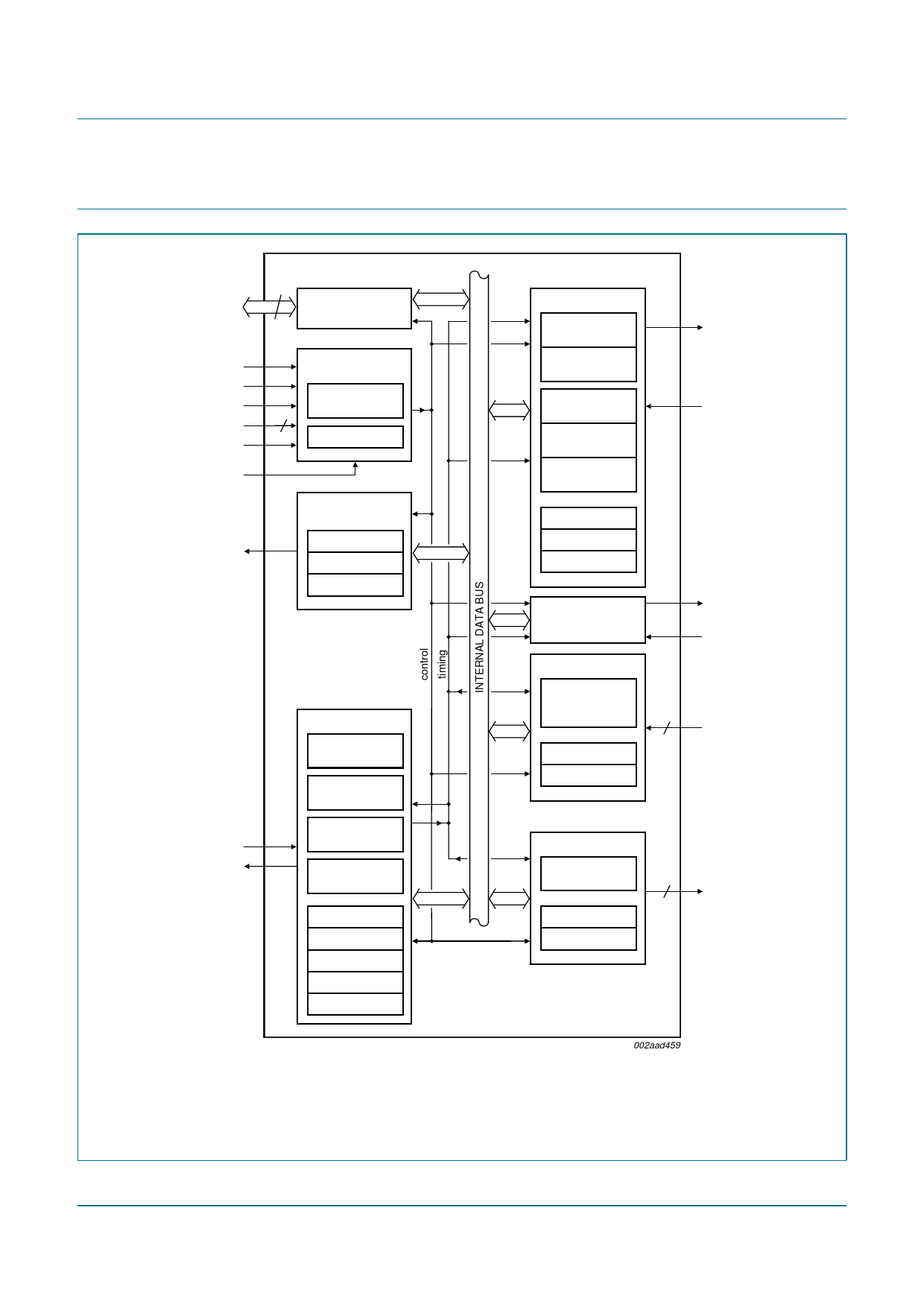

4. Block diagram

SC28L92

3.3 V/5.0 V Dual Universal Asynchronous Receiver/Transmitter

D0 to D7

SC28L92 (80xxx mode)

8

BUS BUFFER

RDN

WRN

CEN

A0 to A3

RESET

I/M

open or connect

to VCC for 80xxx

INTRN

OPERATION

CONTROL

ADDRESS

DECODE

4

R/W CONTROL

INTERRUPT

CONTROL

IMR

ISR

GP

X1/CLK

X2

TIMING

BAUD RATE

GENERATOR

CLOCK

SELECTORS

COUNTER/

TIMER

XTAL

OSCILLATOR

CSRA

CSRB

ACR

CTL

CTU

CHANNEL A

16-BYTE

TRANSMIT FIFO

TRANSMIT

SHIFT REGISTER

16-BYTE

RECEIVE FIFO

WATCHDOG

TIMER

RECEIVE

SHIFT REGISTER

MRA0, 1, 2, 3

CRA

SRA

CHANNEL B

(AS ABOVE)

INPUT PORT

CHANGE-OF-

STATE

DETECTORS (4)

7

IPCR

ACR

TxDA

RxDA

TxDB

RxDB

IP0 to IP6

OUTPUT PORT

FUNCTION

SELECT LOGIC

8

OPCR

OPR

OP0 to OP7

002aad459

The data pins TxD and RxD are considered idle at the logic 1 (HIGH) level when inactive, or active when at the logic 0

(LOW) level. Comments about these levels when RS232 is referenced often refer to Mark and Space levels. Mark usually

means inactive and Space means active. The voltage levels represented by the terms Mark and Space are often reversed

from those above: Mark is low voltage, and Space is high voltage.

Fig 1. Block diagram (80xxx mode)

SC28L92_7

Product data sheet

Rev. 07 — 19 December 2007

© NXP B.V. 2007. All rights reserved.

4 of 73