74HCT166(2015) View Datasheet(PDF) - NXP Semiconductors.

Part Name

Description

MFG CO.

74HCT166 Datasheet PDF : 20 Pages

| |||

Nexperia

74HC166; 74HCT166

8-bit parallel-in/serial out shift register

6. Functional description

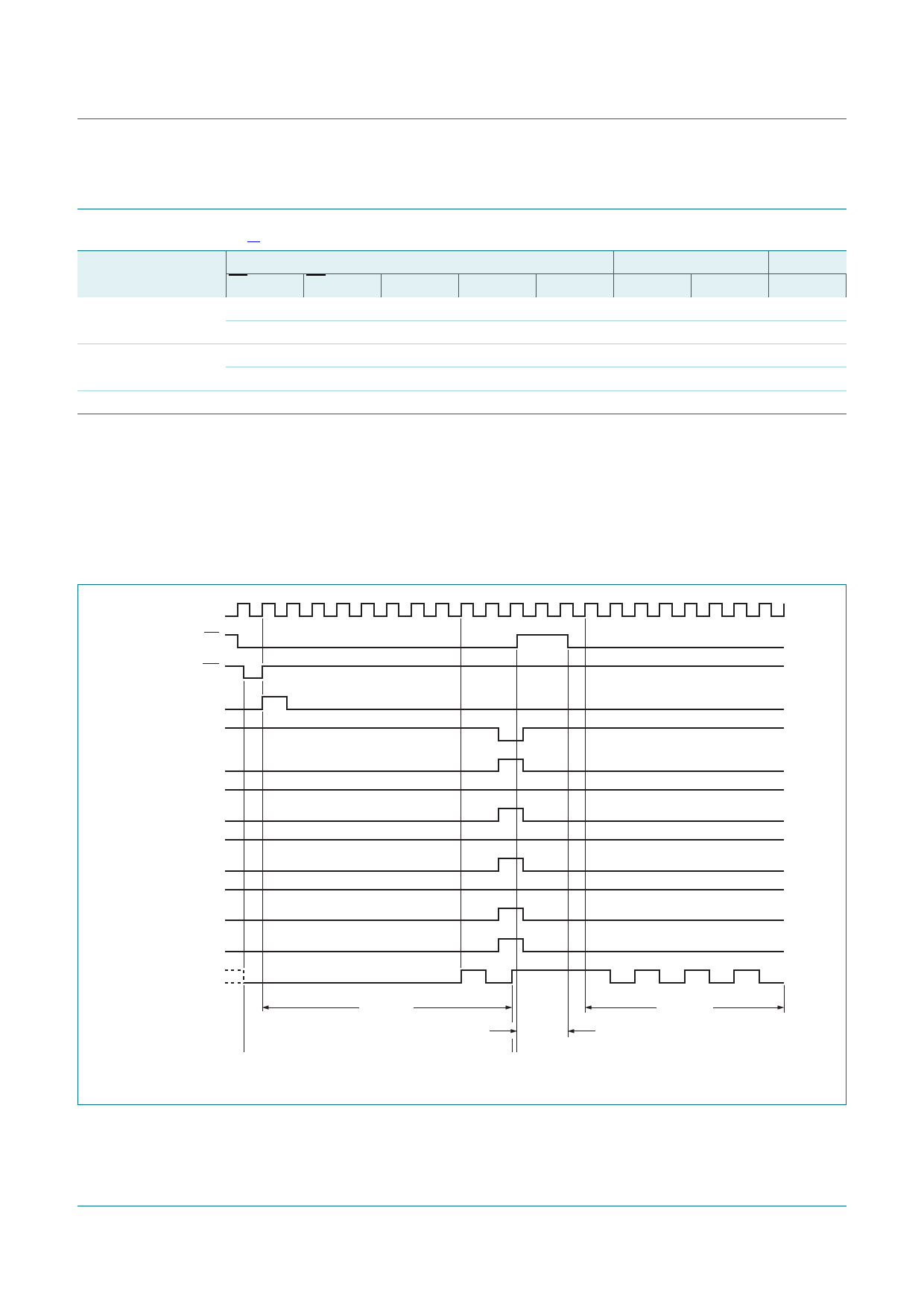

Table 3. Function table[1]

Operating modes Inputs

Qn registers

Output

PE

CE

CP

DS

D0 to D7 Q0

Q1 to Q6 Q7

parallel load

I

I

X

I

L

L to L

L

I

I

X

h

H

H to H

H

serial shift

h

I

l

X

L

q0 to q5 q6

h

I

h

X

H

q0 to q5 q6

hold “do nothing”

X

H

X

X

X

q0

q1 to q6 q7

[1] H = HIGH voltage level;

h = HIGH voltage level one set-up time prior to the LOW-to-HIGH clock transition;

L = LOW voltage level;

l = LOW voltage level one set-up time prior to the LOW-to-HIGH clock transition;

q = state of the referenced output one set-up time prior to the LOW-to-HIGH clock transition;

X = don’t care;

= LOW-to-HIGH clock transition.

&3

PRGH

FRQWURO

&(

LQSXWV

05

SDUDOOHO

LQSXWV

'6

VKLIW

ORDG

'

'

'

'

'

'

'

'

RXWSXW

4

VHULDOVKLIW

+

/

+

/

+

/

+

+

++ / + / + / +

LQKLELW

VHULDOVKLIW

FOHDU

ORDG

DDD

Fig 6. Typical clear, shift, load, inhibit, and shift sequences

74HC_HCT166

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 4 — 28 December 2015

© Nexperia B.V. 2017. All rights reserved

5 of 20