HEF40106BT,653 View Datasheet(PDF) - NXP Semiconductors.

Part Name

Description

MFG CO.

HEF40106BT,653 Datasheet PDF : 16 Pages

| |||

NXP Semiconductors

HEF40106B

Hex inverting Schmitt trigger

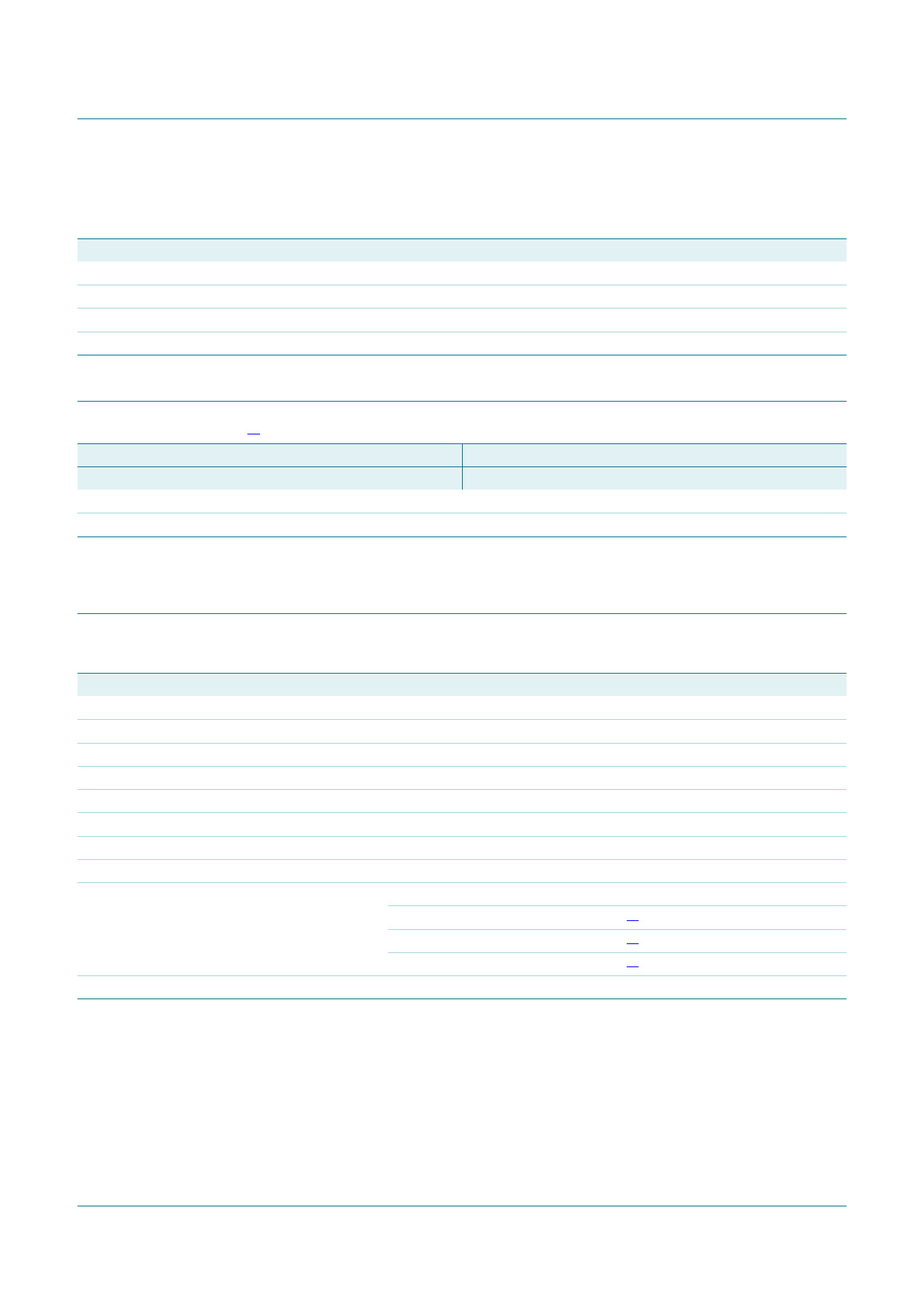

6.2 Pin description

Table 2.

Symbol

1A to 6A

1Y to 6Y

VDD

VSS

Pin description

Pin

1, 3, 5, 9, 11, 13

2, 4, 6, 8, 10, 12

14

7

Description

input

output

supply voltage

ground (0 V)

7. Functional description

Table 3.

Input

nA

L

H

Function table[1]

[1] H = HIGH voltage level; L = LOW voltage level.

8. Limiting values

Output

nY

H

L

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to VSS = 0 V (ground).

Symbol Parameter

Conditions

Min

Max

Unit

VDD

IIK

VI

IOK

II/O

IDD

Tstg

Tamb

Ptot

supply voltage

input clamping current

input voltage

output clamping current

input/output current

supply current

storage temperature

ambient temperature

total power dissipation

VI < 0.5 V or VI > VDD + 0.5 V

VO < 0.5 V or VO > VDD + 0.5 V

Tamb = 40 C to +125 C

DIP14

0.5

-

0.5

-

-

-

65

40

[1] -

+18

V

10

mA

VDD + 0.5 V

10

mA

10

mA

50

mA

+150

C

+125

C

750

mW

SO14

[2] -

500

mW

TSSOP14

[3] -

500

mW

P

power dissipation

per output

-

100

mW

[1] For DIP14 packages: above Tamb = 70 C, Ptot derates linearly with 12 mW/K.

[2] For SO14 packages: above Tamb = 70 C, Ptot derates linearly with 8 mW/K.

[3] For TSSOP14 packages: above Tamb = 60 C, Ptot derates linearly with 5.5 mW/K.

HEF40106B

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 6 — 23 August 2011

© NXP B.V. 2011. All rights reserved.

3 of 16