NM24C16TLVMT8 View Datasheet(PDF) - Fairchild Semiconductor

Part Name

Description

MFG CO.

NM24C16TLVMT8 Datasheet PDF : 14 Pages

| |||

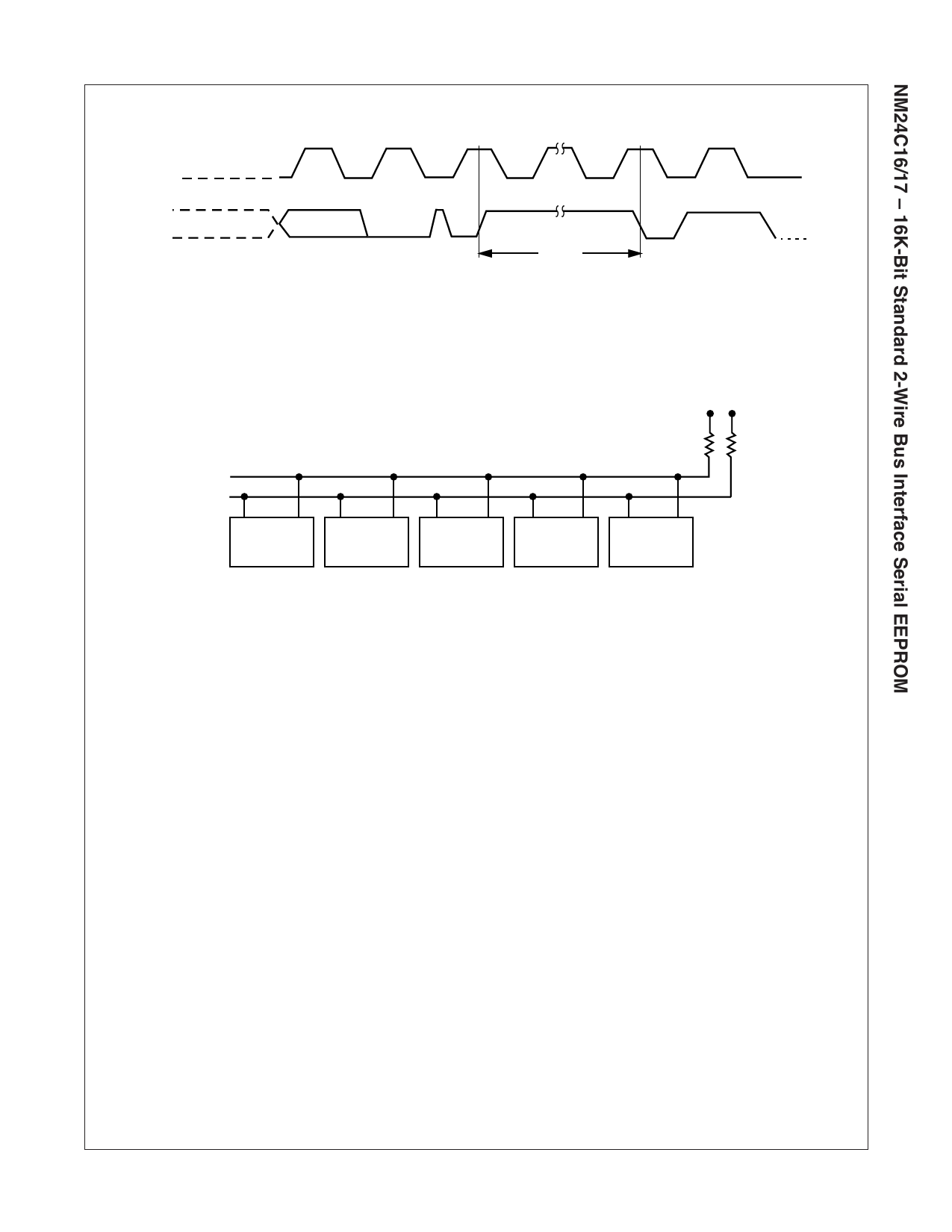

Write Cycle Timing

SCL

SDA

8th BIT

ACK

Note:

WORD n

STOP

CONDITION

tWR

START

CONDITION

The write cycle time (tWR) is the time from a valid stop condition of a write sequence to the end of the internal erase/program cycle.

DS500072-8

Typical System Configuration

VCC

VCC

SDA

SCL

Master

Transmitter/

Receiver

Slave

Receiver

Slave

Transmitter/

Receiver

Master

Transmitter

Master

Transmitter/

Receiver

Note: Due to open drain configuration of SDA and SCL, a bus-level pull-up resistor is called for, (typical value = 4.7kΩ)

DS500072-9

NM24C16/17 Rev. G

6

www.fairchildsemi.com