LH7A400 View Datasheet(PDF) - Sharp Electronics

Part Name

Description

MFG CO.

LH7A400 Datasheet PDF : 53 Pages

| |||

LH7A400

32-Bit System-on-Chip

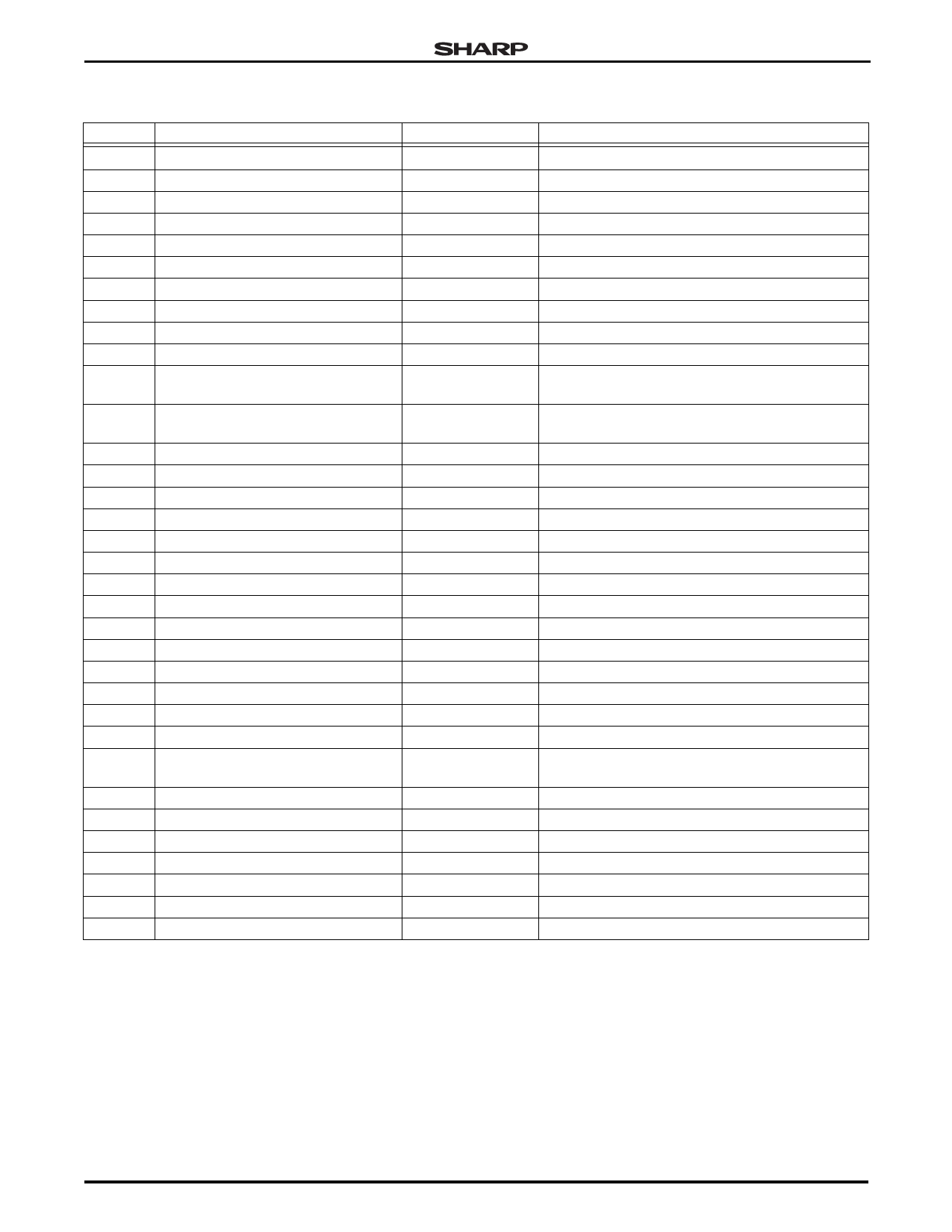

Table 4. 256-Ball PBGA Package Numerical Pin List (Cont’d)

BGA PIN

SIGNAL

P15 XTAL32OUT

P16 XTAL32IN

R1 PC2/LCDVDDEN

R2 PC7/LCDSPL

R3 PG0/nPCOE

R4 PH1/CFA8/PCRESET2

R5 PH6/nAC97RESET

R6 LCDFP

R7 LCDVD1

R8 LCDLP

R9 PD4/LCDVD12

R10 PD7/LCDVD15

R11 VDDA

R12 WIDTH1

R13 XTALIN

R14 VDD

R15 nTEST1

R16 VSS

T1 PC5/LCDCLS

T2 PC6/LCDHRLP

T3 PG1/nPCWE

T4 PH2/nPCSLOTE1

T5 PH7/nPCSTATRE

T6 VDD

T7 LCDVD2

T8 VDDC

T9 PD5/LCDVD13

T10 VSSC

T11 VSSA

T12 nTEST0

T13 XTALOUT

T14 VSS

T15 USBDP

T16 USBDN

RESET STATE

Output

Input

LOW: PC2

LOW: PC7

LOW: PG0

Input: PH1

Input: PH6

LOW

LOW

LOW

LOW: PD4

LOW: PD7

STANDBY STATE

Output

Input

No Change

No Change

No Change

No Change

No Change

LOW

LOW

LOW

LOW if Dual-Panel LCD is Enabled; otherwise,

No Change

LOW if Dual-Panel LCD is Enabled; otherwise,

No Change

Input

Input

Input

Input

Input with Pull-up Input with Pull-up

LOW: PC5

LOW: PC6

LOW: PG1

Input: PH2

Input: PH7

No Change

No Change

No Change

No Change

No Change

LOW

LOW

LOW: PD5

LOW if Dual-Panel LCD is Enabled; otherwise,

No Change

Input with Pull-up

LOW

Input with Pull-up

LOW

HIGH

LOW

HIGH

LOW

NOTE: ‘No Change’ means the pin remains as it was programmed

prior to entering the Standby state.

18

12/8/03

Preliminary Data Sheet