L9310 View Datasheet(PDF) - Agere -> LSI Corporation

Part Name

Description

MFG CO.

L9310

Agere -> LSI Corporation

L9310 Datasheet PDF : 60 Pages

| |||

Data Sheet

July 2001

L9310 Line Interface and Line Access Circuit

Full-Feature SLIC, Ringing Relay, and Test Access Device

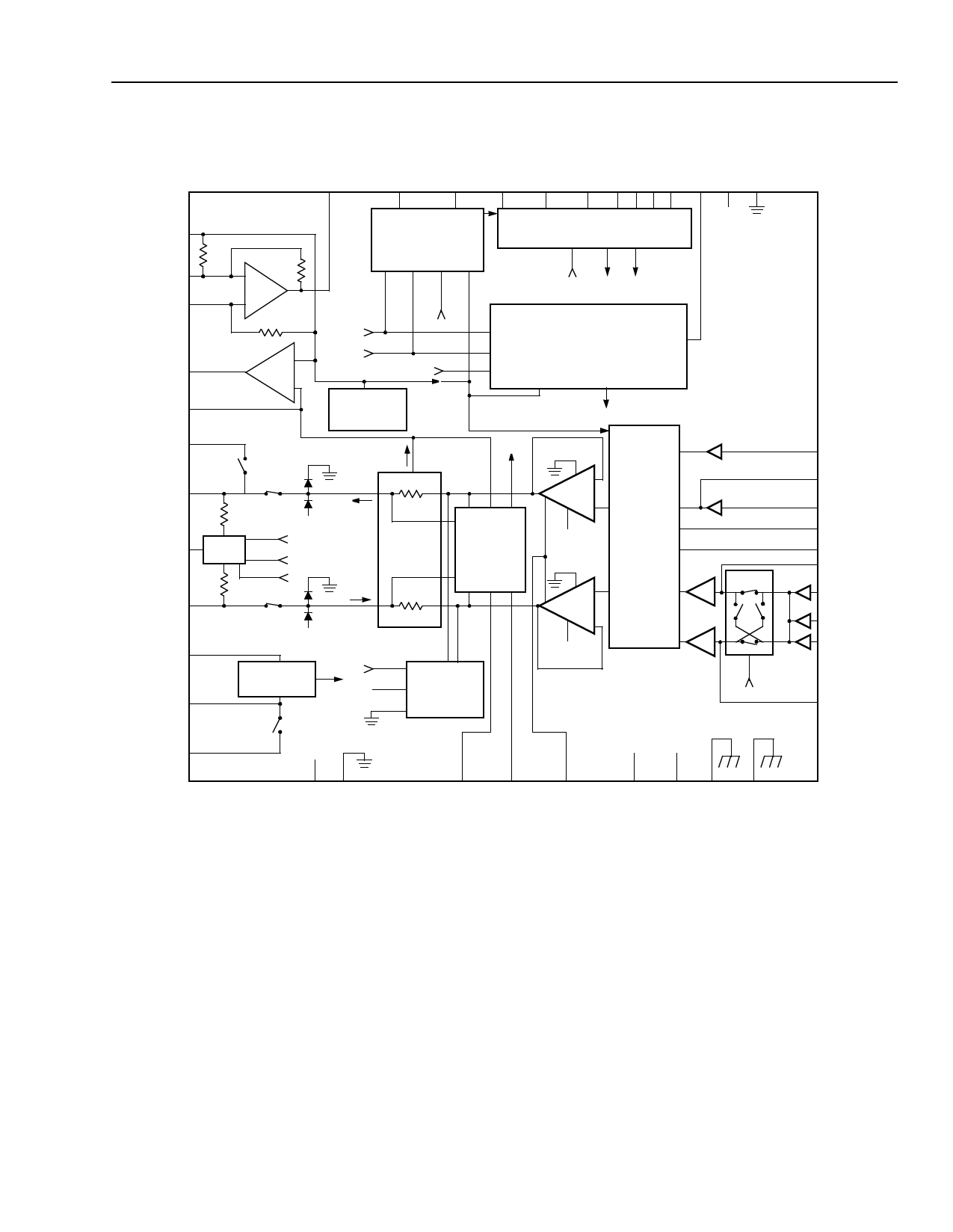

Architecture

VITR

LCF

LCTH RESET NSTAT LATCH B3 B2 B1 B0 VPROG VDD DGND

VREF

TXN

TXI

–

AAC

+

VTX

(1 V/50 mA)

ITR

+

AX

–

SWITCHHOOK

WINDOW

COMPARATOR

IN REF

PARALLEL DATA INTERFACE

RT CONTROL

FB

ILC

RB

VTX

2.35 V

BANDGAP

REFERENCE

2.35 V

VREF

CURRENT LIMITER

AND

INRUSH CONTROL

IN REF

CF2

CF2

+5VD

TRNG

PT

TESTLEV

PR

RTS

RSW

RRING

SW3

60 Ω

SW1

18 Ω

VITR

TEST VREF

VTX

SW2

18 Ω

BGND ITR/325

RFT

VBAT ITR

BGND

TIP/RING

CURRENT

SENSE

ITR

RFR

ILC

SCAN

&

RING GND

DETECTOR

VBAT

RING TRIP RT

DETECTOR

SW4

15 Ω

+5VA

SCAN

VBAT

BGND

SCAN

CLAMP

BGND

+

OUT AT

–

VBAT

ac

INTERFACE ac

BGND

+

OUT AR

–

VBAT

x1

dc

x1

VBAT

FBRB

FB

VCC AGND

TRGDET ICM VBAT2/PWR

VBAT1 VBAT1 BGND BGND

Figure 1. Architecture Diagram

TESTSIG

PPMOUT

PPMIN

RCVP

RCVN

FB1

CF1

OVH

CF2

FB2

12-3523 (F)

Agere Systems Inc.

9