AD7322BRU View Datasheet(PDF) - Atmel Corporation

Part Name

Description

MFG CO.

AD7322BRU Datasheet PDF : 18 Pages

| |||

AD7322

Preliminary Technical Data

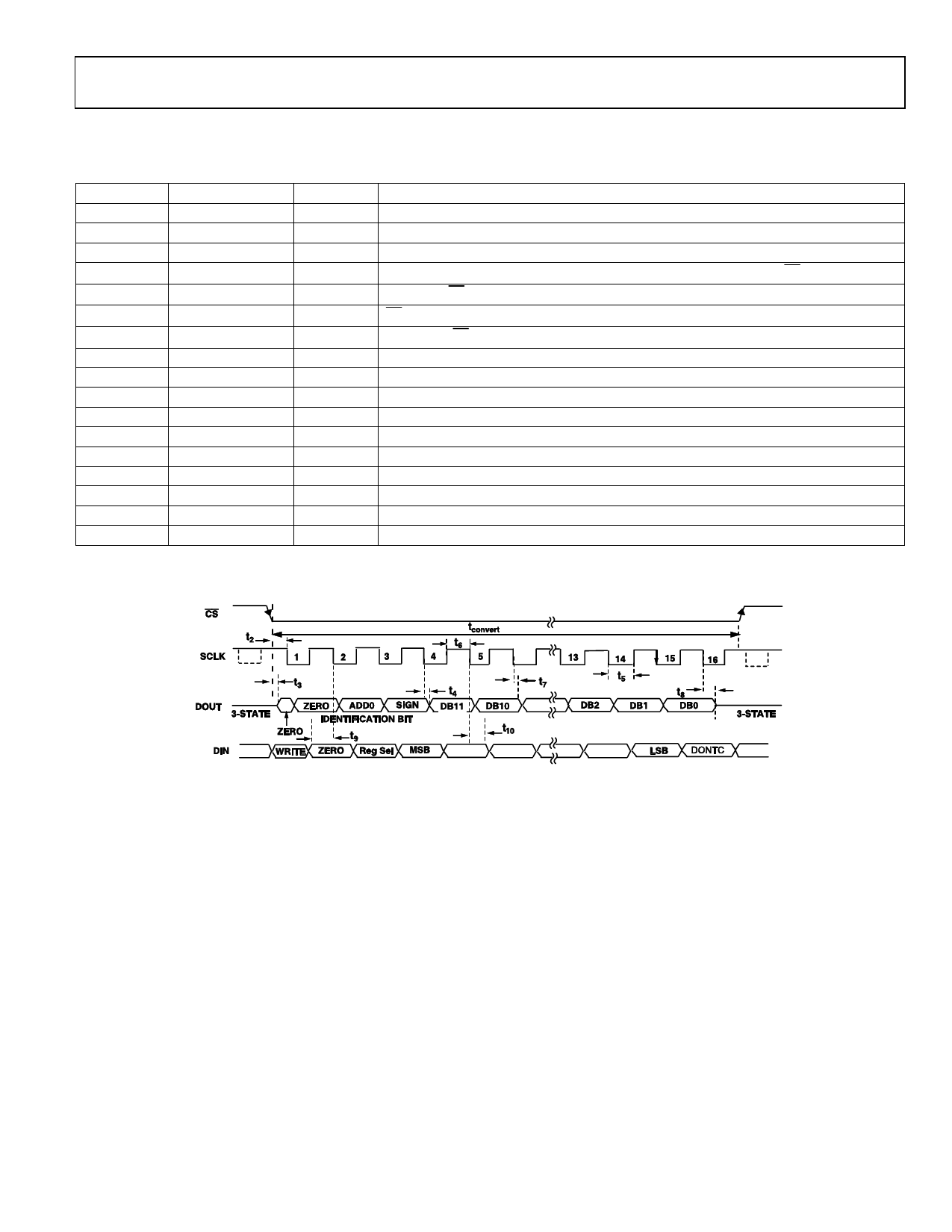

TIMING SPECIFICATIONS

Table 2. Unless otherwise noted, VDD = +4.75V to + 16.5V, VSS = -4.75 to –16.5V, VCC =2.7V to 5.25, VDRIVE=2.7V to 5.25, VREF =

2.5V Internal/External, TA = TMAX to TMIN

Parameter Limit at TMIN, TMAX Unit

Description

fSCLK

10

kHz min

20

MHz max

tCONVERT

16×tSCLK

ns max

TSCLK = 1/fSCLK

tQUIET

50

ns max

Minimum Time between End of Serial Read and Next Falling Edge of CS

t1

10

ns min

Minimum CS Pulse width

t2

10

ns min

CS to SCLK Setup Time

t3

20

ns max

Delay from CS until DOUT Three-State Disabled

t4

TBD

ns max

Data Access Time after SCLK Falling Edge.

t5

0.4tSCLK

ns min

SCLK Low Pulsewidth

t6

0.4tSCLK

ns min

SCLK High Pulsewidth

t7

10

ns min

SCLK to Data Valid Hold Time

t8

25

ns max

SCLK Falling Edge to DOUT High Impedance

10

ns min

SCLK Falling Edge to DOUT High Impedance

t9

TBD

ns min

DIN set-up time prior to SCLK falling edge

t10

5

ns min

DIN hold time after SCLK falling edge

1

µs max

Power up from Auto Standby

TBD

µs max

Power up from Full Shutdown/Auto Shutdown Mode

Figure 2. Serial Interface timing Diagram

Rev. PrE | Page 5 of 18