EPC4XXX View Datasheet(PDF) - Altera Corporation

Part Name

Description

MFG CO.

EPC4XXX Datasheet PDF : 36 Pages

| |||

Functional Description

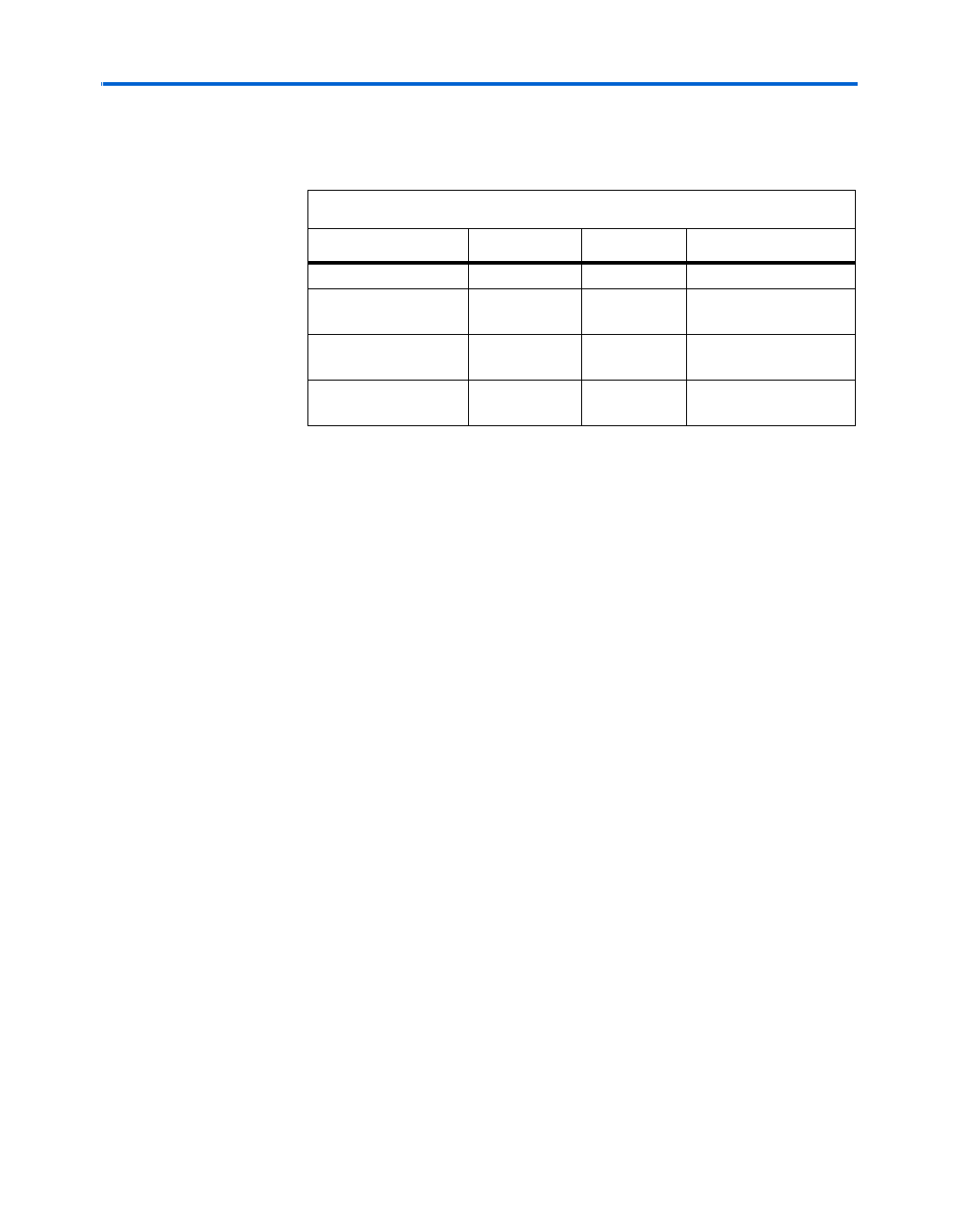

Table 2–4 summarizes the concurrent PS configuration modes supported

in the enhanced configuration device.

f

Table 2–4. Enhanced Configuration Devices in PS Mode

Mode Name

Passive serial mode

Multi-device passive

serial mode

Multi-device passive

serial mode

Multi-device passive

serial mode

Mode (n =) (1) Used Outputs Unused Outputs

1

DATA0

DATA[7..1] drive low

2

DATA[1..0] DATA[7..2] drive low

4

DATA[3..0] DATA[7..4] drive low

8

DATA[7..0] -

Note to Table 2–4:

(1) This is the number of valid DATA outputs for each configuration mode.

For configuration schematics and more information on concurrent

configuration, refer to Using Altera Enhanced Configuration Devices,

chapter 3 in volume 2 of the Configuration Handbook. or the appropriate

FPGA family chapter in the Configuration Handbook.

f

External Flash Interface

The enhanced configuration devices support external FPGA or processor

access to its flash memory. The unused portions of the flash memory can

be used by the external device to store code or data. This interface can also

be used in systems that implement remote configuration capabilities.

Configuration data within a particular configuration page can be

updated via the external flash interface and the system could be

reconfigured with the new FPGA image. This interface is also useful to

store Nios boot code and/or application code.

For more information on the Stratix remote configuration feature, refer

to the Using Remote System Configuration with Stratix & Stratix GX Devices

chapter of the Stratix Device Handbook.

The address, data, and control ports of the flash memory are internally

connected to the enhanced configuration device controller and to external

device pins. An external source can drive these external device pins to

access the flash memory when the flash interface is available.

This external flash interface is a shared bus interface with the

configuration controller chip. The configuration controller is the primary

bus master. Since there is no bus arbitration support, the external device

can only access the flash interface when the controller has tri-stated its

2–12

Configuration Handbook, Volume 2

Altera Corporation

August 2005