EP1C3F400I6ES View Datasheet(PDF) - Unspecified

Part Name

Description

MFG CO.

EP1C3F400I6ES Datasheet PDF : 94 Pages

| |||

Cyclone FPGA Family Data Sheet

Preliminary Information

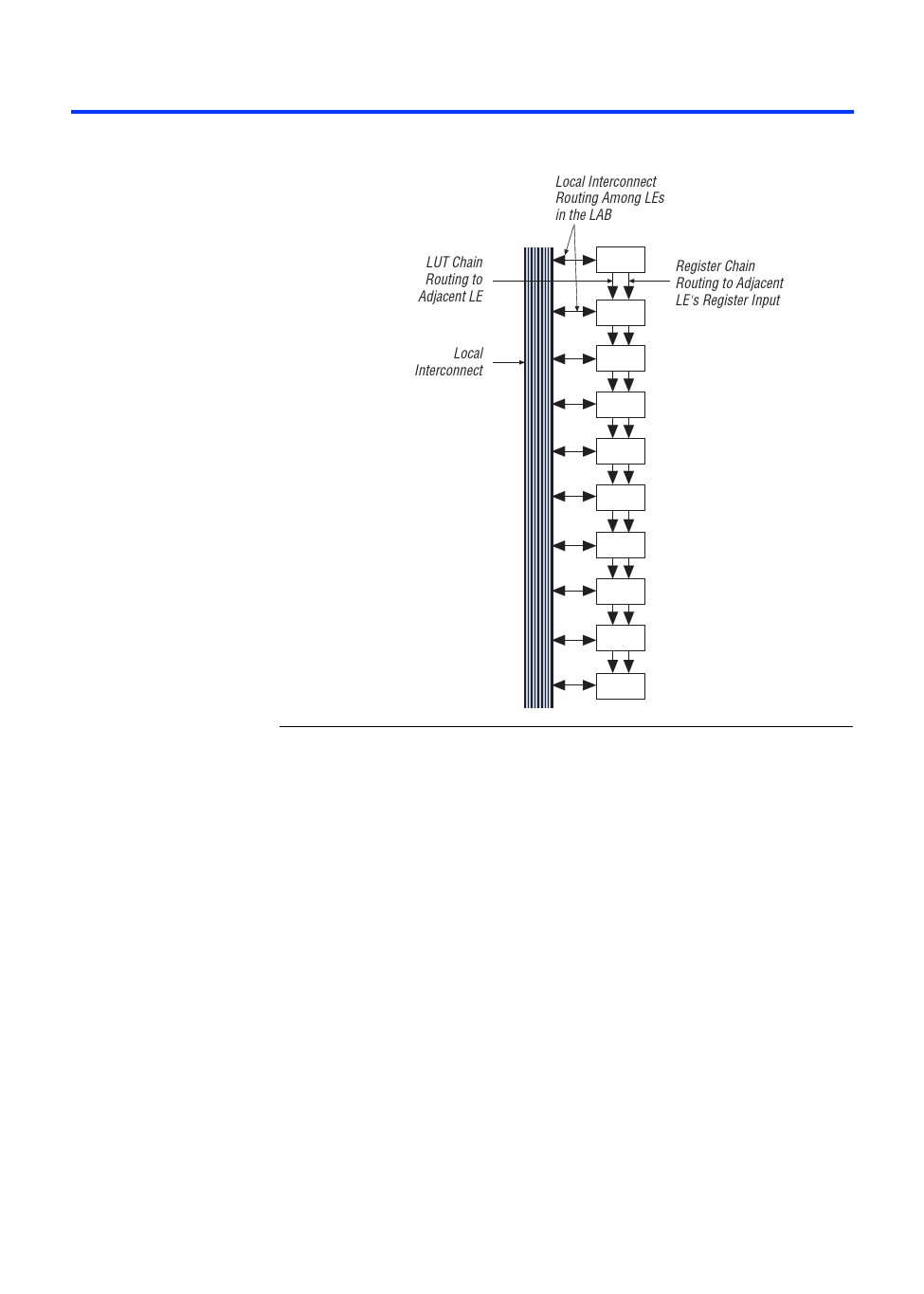

Figure 10. LUT Chain & Register Chain Interconnects

Local Interconnect

Routing Among LEs

in the LAB

LUT Chain

Routing to

Adjacent LE

Local

Interconnect

LE 1

LE 2

LE 3

LE 4

Register Chain

Routing to Adjacent

LE's Register Input

LE 5

LE 6

LE 7

LE 8

LE 9

LE 10

The C4 interconnects span four LABs or M4K blocks up or down from a

source LAB. Every LAB has its own set of C4 interconnects to drive either

up or down. Figure 11 shows the C4 interconnect connections from an

LAB in a column. The C4 interconnects can drive and be driven by all

types of architecture blocks, including PLLs, M4K memory blocks, and

column and row IOEs. For LAB interconnection, a primary LAB or its LAB

neighbor can drive a given C4 interconnect. C4 interconnects can drive

each other to extend their range as well as drive row interconnects for

column-to-column connections.

20

Altera Corporation