MAS9116ASBA View Datasheet(PDF) - Micro Analog systems

Part Name

Description

MFG CO.

MAS9116ASBA Datasheet PDF : 18 Pages

| |||

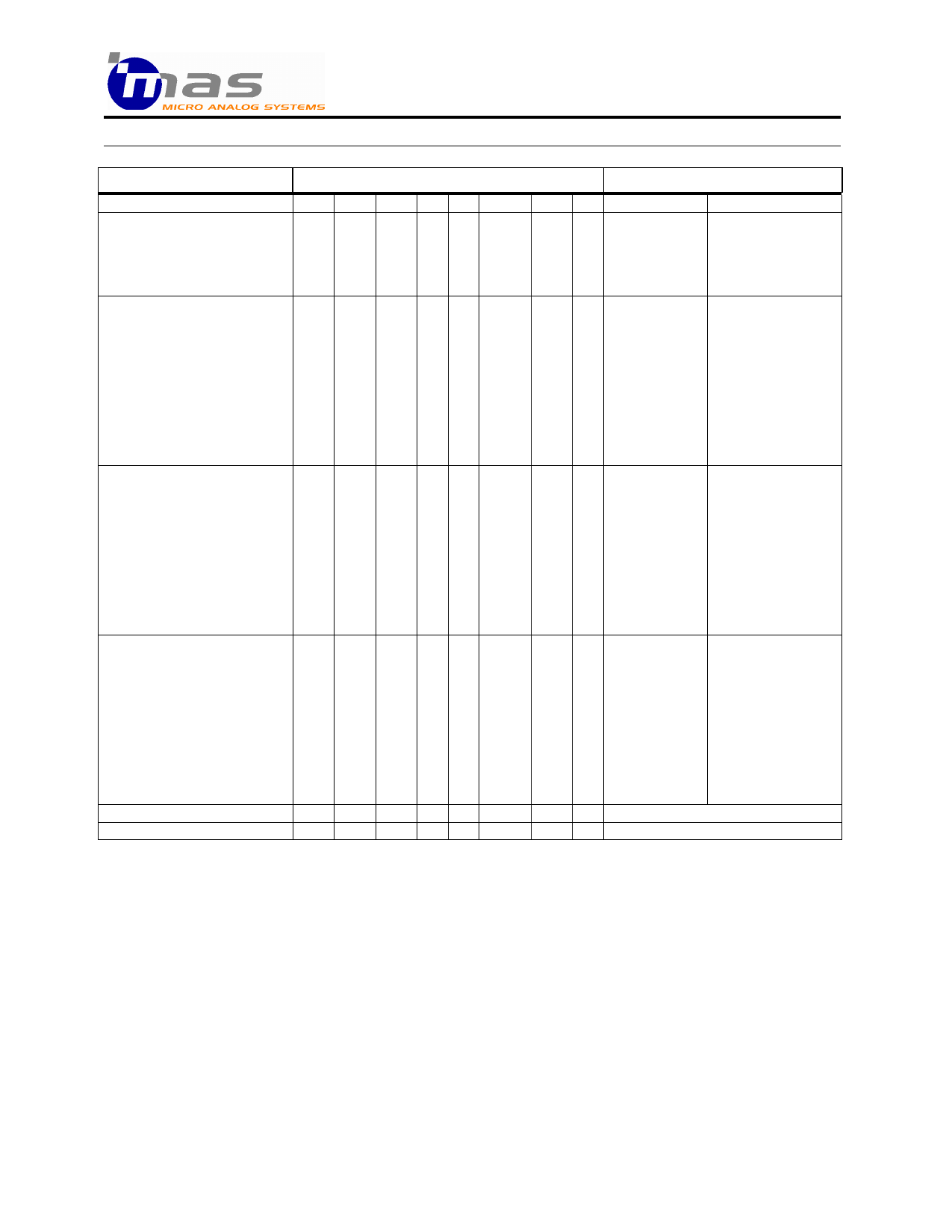

REGISTER DESCRIPTION

DA9116.005

22 November, 2005

Register

Peak Detector Status

CR4

Address Byte

7 6 5 43 2

10

X 1 0 1 1 R/W X X

Peak Detector Reference

CR3

X 1 1 0 0 R/W X X

Left Channel Gain

CR2

X 1 1 0 1 R/W X X

Right Channel Gain

CR1

X 1 1 1 0 R/W X X

Test, CR5

X 1 1 1 1 R/W X X

Both Channel Gains

X 1 0 01 W X X

Note 1. Reference voltage is calculated from VREF(CODE)=(0.16+0.0133*CODE)*VDD

Data Byte

msb…lsb

Function

Output code

00000000

No overload

00000001

Right overload

00000010

Left overload

00000011

Both overload

Input code

DAC output

11111111

VREF(255)

11111110

VREF(254)

11111101

VREF(253)

•

•

•

•

00000010

VREF(2)

00000001

VREF(1)

00000000

VREF(0)

Note 1

Input code

Gain dB

11111111

+15.5

11111110

+15.0

11111101

+14.5

•

•

•

•

11100000

0.0

00000010

-111.0

00000001

-111.5

00000000

mute

Input code

Gain dB

11111111

+15.5

11111110

+15.0

11111101

+14.5

•

•

•

•

11100000

0.0

00000010

-111.0

00000001

-111.5

00000000

mute

Reserved

Write to both gain registers

Address byte bits:

• Bit 2 is read/write bit (1=read, 0=write).

• X is don’t care, recommended high for low

power.

Data byte bits:

• All registers get their default value 00Hex except

CR3 which gets FFHex during power-on reset.

• Default value for all bits is zero (00hex).

5 (18)