M74HC195 View Datasheet(PDF) - STMicroelectronics

Part Name

Description

View to exact match

M74HC195 Datasheet PDF : 12 Pages

| |||

M74HC195

4 BIT PIPO SHIFT REGISTER

s HIGH SPEED :

tPD = 14 ns (TYP.) at VCC = 6V

s LOW POWER DISSIPATION:

ICC =4µA(MAX.) at TA=25°C

s HIGH NOISE IMMUNITY:

VNIH = VNIL = 28 % VCC (MIN.)

s SYMMETRICAL OUTPUT IMPEDANCE:

|IOH| = IOL = 4mA (MIN)

s BALANCED PROPAGATION DELAYS:

tPLH ≅ tPHL

s WIDE OPERATING VOLTAGE RANGE:

VCC (OPR) = 2V to 6V

s PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 195

DESCRIPTION

The M74HC195 is an high speed CMOS 4 BIT

PIPO SHIFT REGISTER fabricated with silicon

gate C2MOS technology.

This shift register features parallel inputs, parallel

outputs, J-K serial inputs, a SHIFT/LOAD control

input, and direct overriding CLEAR. This shift

register can operate in two modes : Parallel Load;

Shift from QA towards QD.

Parallel loading is accomplished by applying the

four bits of data , and taking the SHIFT/LOAD (S/

L) control input low. The data is loaded into the

associated flip-flops and appears at the outputs

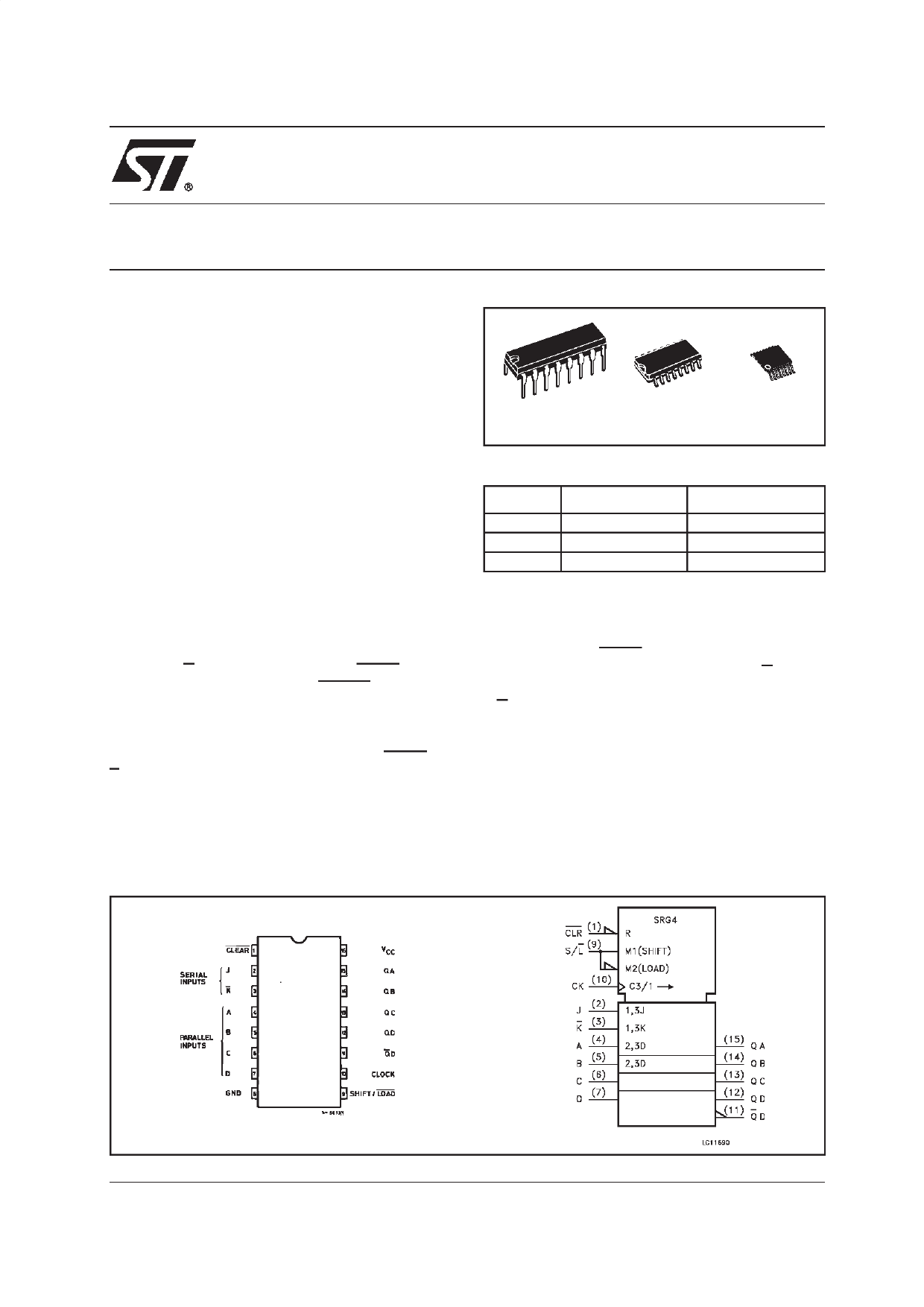

DIP

SOP

TSSOP

ORDER CODES

PACKAGE

TUBE

DIP

SOP

TSSO P

M74HC195B1R

M74HC195M1R

T&R

M74HC195RM13TR

M74HC195TTR

after the positive transition of the clock input.

During parallel loading, serial data flow is

inhibited. Serial shifting occurs synchronously

when the SHIFT/LOAD control input is high. Serial

data for this mode is entered at the J-K inputs.

These inputs allow the first stage to perform as a

J-K or TOGGLE flip-flop as shown in the truth

table.

All inputs are equipped with protection circuits

against static discharge and transient excess

voltage.

PIN CONNECTION AND IEC LOGIC SYMBOLS

August 2001

1/12