VP5513 View Datasheet(PDF) - Mitel Networks

Part Name

Description

View to exact match

VP5513 Datasheet PDF : 19 Pages

| |||

VP5313/VP5513

IICEXCTL

CTL7-0

I2C Extension Control

Each bit controls port direction

0 = output 1 = input

IICEXR/W

RD7-0

I2C Extension Control

I2C bus read and write data from

I2C extension port

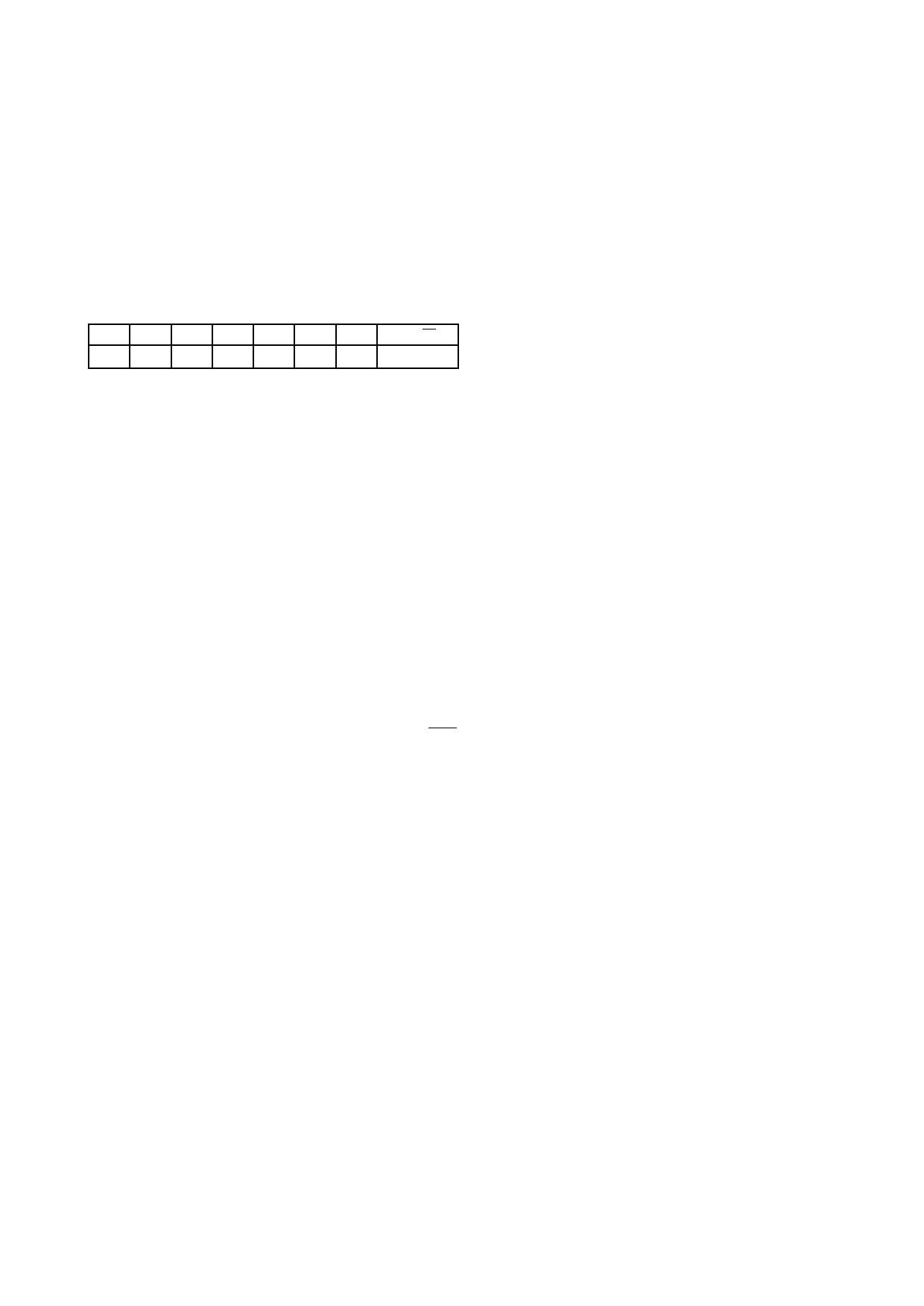

I2C BUS CONTROL INTERFACE

I2C bus address

A6 A5 A4 A3 A2 A1 A0

0 0 0 1 1 0 SA

R/ W

X

The serial microprocessor interface is via the bi-directional

port consisting of a data (SDA) and a clock (SCL) line. It is

compatible to the Philips I2C bus standard (Jan. 1992

publication number 9398 393 40011). The interface is a slave

transmitter - receiver with a sub-address capability. All

communication is controlled by the microprocessor. The SCL

line is input only. The most significant bit (MSB) is sent first.

Data must be stable during SCL high periods.

A bus free state is indicated by both SDA and SCL lines

being high. START of transmission is indicated by SDA being

pulled low while SCL is high. The end of transmission, referred

to as a STOP, is indicated by SDA going from low to high while

SCL is high. The STOP state can be omitted if a repeated

START is sent after the acknowledge bit. The reading device

acknowledges each byte by pulling the SDA line low on the

ninth clock pulse, after which the SDA line is released to allow

the transmitting device access to the bus.

The device address can be partially programmed by the

setting of the pin SA. This allows the device to respond to one

of two addresses, providing for system flexibility. The I2C bus

address is seven bits long with the last bit indicating read/write

for subsequent bytes.

The first data byte sent after the device address, is the sub-

address - BAR (base address register). The next byte will be

written to the register addressed by BAR and subsequent

bytes to the succeeding registers. The BAR maintains its data

after a STOP signal.

NTSC/PAL Video Standards

Both NTSC (4-field, 525 lines) and PAL (8-field, 625 lines)

video standards are supported by the VP5313/VP5513. All

raster synchronisation, colour sub-carrier and burst charac-

teristics are adapted to the standard selected. The VP5313/

VP5513 generates outputs which follow the requirements of

SMPTE 170M and CCIR 624 for PAL signals.

The device supports the following standards:

PAL B, D, G, H, I, N (Argentina) (default state) and

NTSC.

Video Blanking

The VP5313/VP5513 automatically performs standard

composite video blanking. Lines 1-9, 264-272 inclusive, as

well as the last half of line 263 are blanked in NTSC mode. In

PAL mode, lines 1-5, 311-318, 624-625 inclusive, as well as

the last half of line 623 are blanked.

The V bit within REC656 defines the video blanking when

in TRS slave mode. By setting VBITDIS in the SLAVE1

register this blanking can be overidden. When in MASTER

mode the V bit is ignored; hence, if any lines are required to be

blank, they must have no video signal input on them.

Interpolator

The luminance and chrominance data is separately

passed through interpolating filters to produce output

sampling rates double that of the incoming pixel rate. This

reduces the sinx/x distortion that is inherent in the digital to

analog converters (DACs), and also simplifies the analog

reconstruction filter requirements.

Digital to Analog Converters

The VP5313/VP5513 contains four 9 bit digital to analog

converters which produce the analog video signals. The

DACs use a current steering architecture in which bit currents

are routed to one of two outputs; thus the DAC has true and

complimentary outputs, however, only the true outputs are

available on the pins. The use of identical current sources and

current steering their outputs means that monoticity is

guaranteed. An on-chip voltage reference of 1·00V (typ.)

provides the necessary biasing; if required, this can be

overridden by an external reference.

The full-scale output currents of the DACs is set by an

external 730Ω resistor between the RREF and AGND pins. An

on-chip loop amplifier stabilises the full-scale output current

against temperature and power supply variations.

By digitally summing the luma and chroma outputs a

composite output is generated. The analog outputs of the

VP5313/VP5513 are capable of directly driving doubly

terminated 75Ω co-axial cable. If it is required only to drive a

single 75Ω load then the DACGAIN resistor is simply doubled.

Luminance, Chrominance and Composite Video Outputs

The Luminance video output drives a 37.5Ω load at 1·0V,

sync tip to peak white. It contains only the luminance content

of the image plus the composite sync pulses. In the NTSC

mode, a set-up level offset is added during the active video

portion of the raster.

The Chrominance video output drives a 37.5Ω load at

levels proportional in amplitude to the luma output (40 IRE pk-

pk burst). Burst is injected with the appropriate timing relative

to the luma signal.

Output sinx/x compensation filters are required on all

video outputs, as shown in the typical application diagram, see

fig. 11 & 12.

RGB Video Outputs

The RGB video outputs drive a 37.5Ω load at 0.7V blank

to peak.

Output sinx/x compensation filters are required on all

video outputs, as shown in the typical application diagram, see

fig. 11 & 12.

Video Timing - Slave sync mode

The VP5313/VP5513 has an internal timing generator

which produces video timing signals appropriate to the mode

of operation. TRS slave mode means that the video encoder

synchronises itself to the TRS (Timing Reference Signal)

codes that are embedded into the Rec. 656 data pattern. In the

9