TC74AC299P(2007) View Datasheet(PDF) - Toshiba

Part Name

Description

View to exact match

TC74AC299P Datasheet PDF : 9 Pages

| |||

TC74AC299P/F

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC74AC299P,TC74AC299F

8-Bit PIPO Shift Register with Asynchronousclear

The TC74AC299 is an advanced high speed CMOS 8-BIT PIPO

SHIFT REGISTER fabricated with silicon gate and double-layer

metal wiring C2MOS technology.

It achieves the high speed operation similar to equivalent

Bipolar Schottky TTL while maintaining the CMOS low power

dissipation.

It has a four modes (HOLD, SHIFT LEFT, SHIFT RIGHT and

LOAD DATA) controlled by the two selection inputs (S0, S1).

When one or both enable ( G1 , G2 ) are high, the eight I/O

outputs are forced to the high-impedance state; however,

sequential operation or clearing of the register is not affected.

All inputs are equipped with protection circuits against static

discharge or transient excess voltage.

TC74AC299P

TC74AC299F

Features (Note 1)(Note 2)

• High speed: fmax = 150 MHz (typ.) at VCC = 5 V

• Low power dissipation: ICC = 8 μA (max) at Ta = 25°C

• High noise immunity: VNIH = VNIL = 28% VCC (min)

• Symmetrical output impedance: |IOH| = IOL = 24 mA (min)

Capability of driving 50 Ω

tansmission lines.

• Balanced propagation delays: tpLH ∼− tpHL

• Wide operating voltage range: VCC (opr) = 2 to 5.5 V

• Pin and function compatible with 74F299

Weight

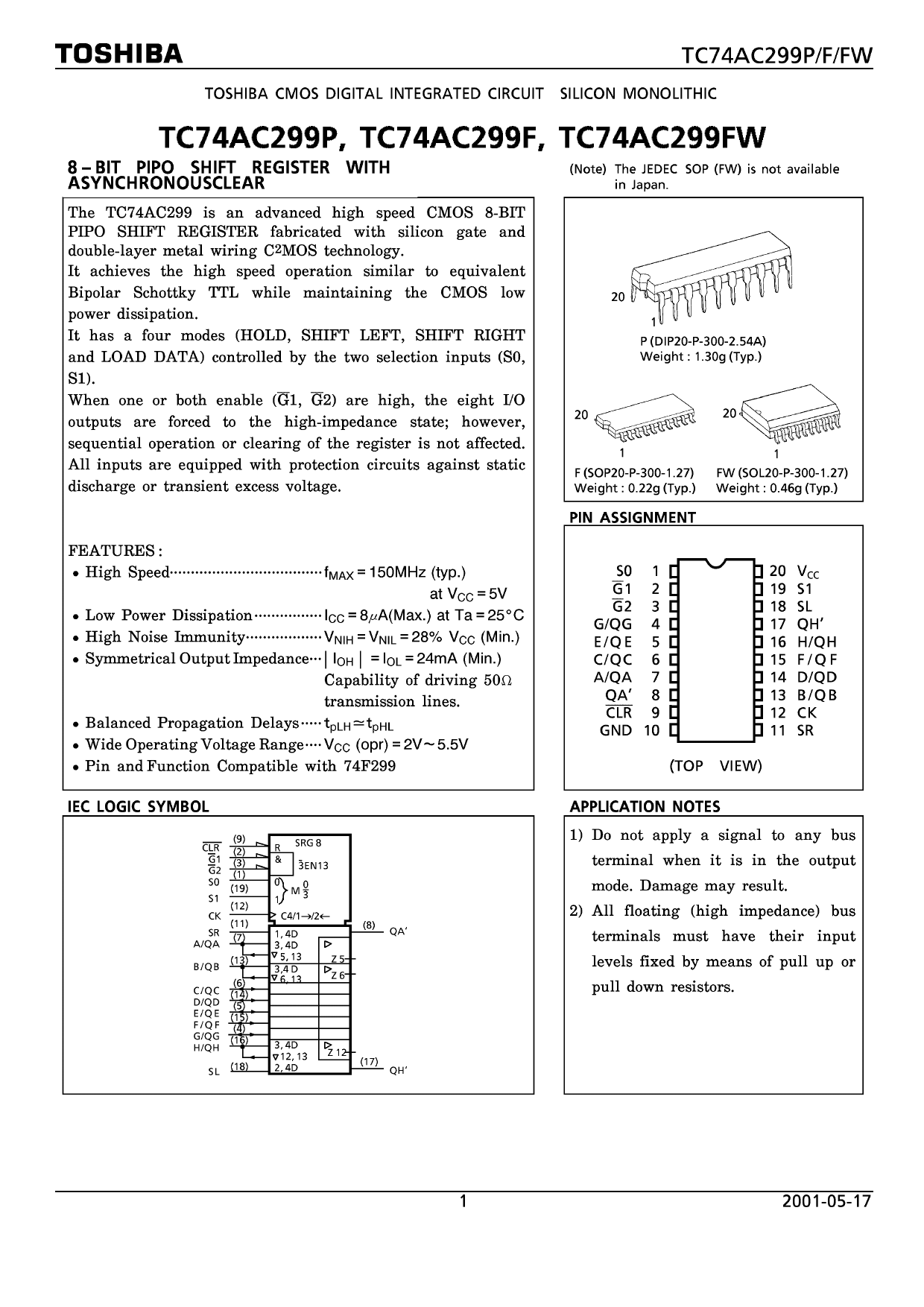

DIP20-P-300-2.54A

SOP20-P-300-1.27A

: 1.30 g (typ.)

: 0.22 g (typ.)

Note 1: Do not apply a signal to any bus terminal when it is in the output mode. Damage may result.

Note 2: All floating (high impedance) bus terminals must have their input levels fixed by means of pull up or pull

down resistors.

Pin Assignment

1

2007-10-01