SST89E58RD2(2007) View Datasheet(PDF) - Silicon Storage Technology

Part Name

Description

View to exact match

SST89E58RD2 Datasheet PDF : 81 Pages

| |||

FlashFlex MCU

SST89E54RD2/RD / SST89E58RD2/RD

SST89V54RD2/RD / SST89V58RD2/RD

Caution must be taken when dynamically changing the

SFCF[0] bit. Since this will cause different physical memory

to be mapped to the logical program address space. The

user must avoid executing block switching instructions

within the address range 0000H to 1FFFH.

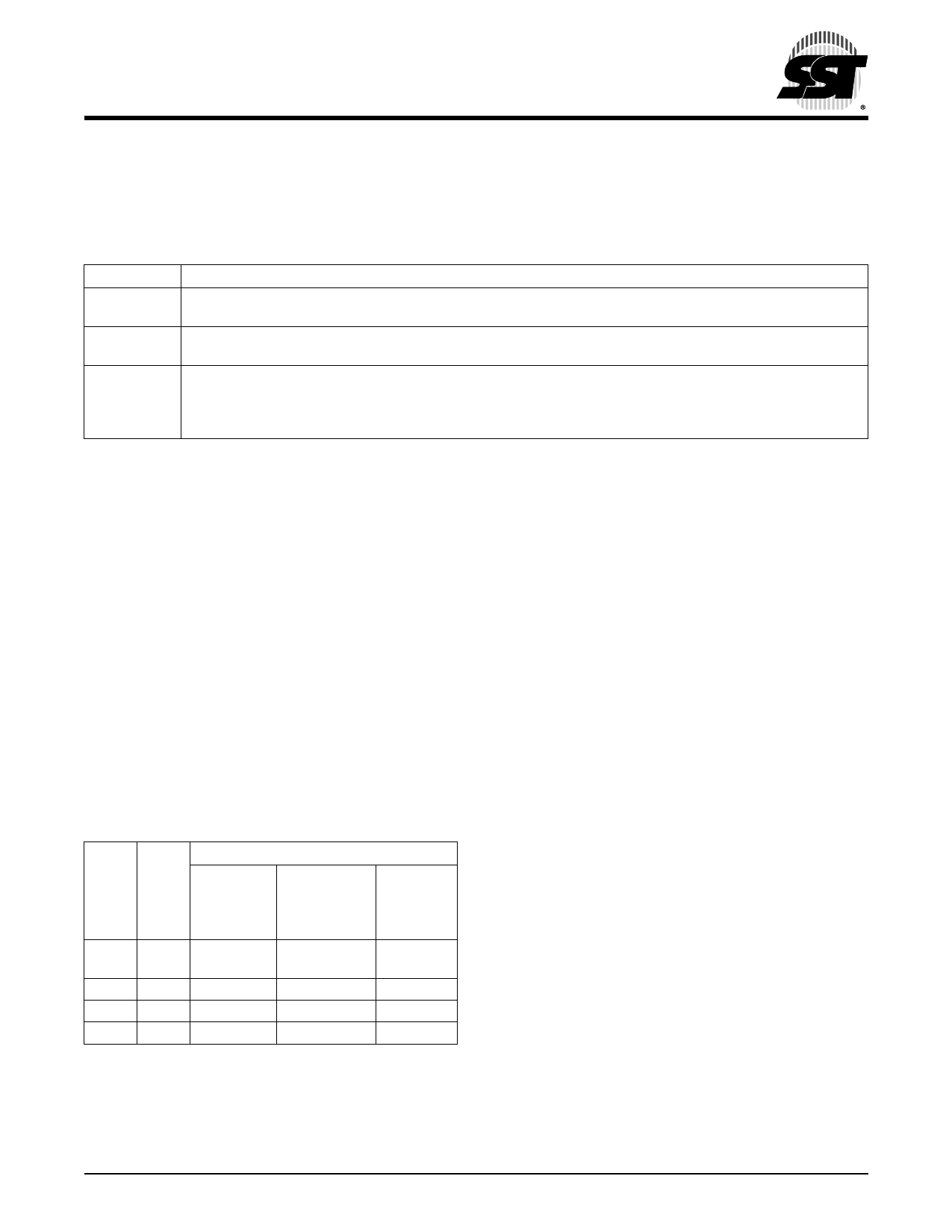

TABLE 3-2: SFCF Values Under Different Reset

Conditions

State of SFCF[1:0] after:

SC11 SC01

U (1) U (1)

U (1)

P (0)

P (0)

P (0)

U (1)

P (0)

Power-on

or

External

Reset

00

(default)

01

10

11

WDT Reset

or

Brown-out

Reset

x0

x1

10

11

1. P = Programmed (Bit logic state = 0),

U = Unprogrammed (Bit logic state = 1)

Software

Reset

10

11

10

11

T3-2.0 1255

3.3 Data RAM Memory

The data RAM has 1024 bytes of internal memory. The

RAM can be addressed up to 64KB for external data

memory.

3.4 Expanded Data RAM Addressing

The SST89E/V5xRDx both have the capability of 1K of

RAM. See Figure 3-3.

The device has four sections of internal data memory:

1. The lower 128 Bytes of RAM (00H to 7FH) are

directly and indirectly addressable.

2. The higher 128 Bytes of RAM (80H to FFH) are

indirectly addressable.

3. The special function registers (80H to FFH) are

directly addressable only.

4. The expanded RAM of 768 Bytes (00H to 2FFH) is

indirectly addressable by the move external

instruction (MOVX) and clearing the EXTRAM bit.

(See “Auxiliary Register (AUXR)” in Section 3.6,

“Special Function Registers”)

Since the upper 128 bytes occupy the same addresses as

the SFRs, the RAM must be accessed indirectly. The RAM

and SFRs space are physically separate even though they

have the same addresses.

Data Sheet

When instructions access addresses in the upper 128

bytes (above 7FH), the MCU determines whether to

access the SFRs or RAM by the type of instruction given. If

it is indirect, then RAM is accessed. If it is direct, then an

SFR is accessed. See the examples below.

Indirect Access:

MOV@R0, #data; R0 contains 90H

Register R0 points to 90H which is located in the upper

address range. Data in “#data” is written to RAM location

90H rather than port 1.

Direct Access:

MOV90H, #data; write data to P1

Data in “#data” is written to port 1. Instructions that write

directly to the address write to the SFRs.

To access the expanded RAM, the EXTRAM bit must be

cleared and MOVX instructions must be used. The extra

768 bytes of memory is physically located on the chip and

logically occupies the first 768 bytes of external memory

(addresses 000H to 2FFH).

When EXTRAM = 0, the expanded RAM is indirectly

addressed using the MOVX instruction in combination

with any of the registers R0, R1 of the selected bank or

DPTR. Accessing the expanded RAM does not affect

ports P0, P3.6 (WR#), P3.7 (RD#), or P2. With

EXTRAM = 0, the expanded RAM can be accessed as

in the following example.

Expanded RAM Access (Indirect Addressing only):

MOVX@DPTR, A; DPTR contains 0A0H

DPTR points to 0A0H and data in “A” is written to address

0A0H of the expanded RAM rather than external memory.

Access to external memory higher than 2FFH using the

MOVX instruction will access external memory (0300H to

FFFFH) and will perform in the same way as the standard

8051, with P0 and P2 as data/address bus, and P3.6 and

P3.7 as write and read timing signals.

When EXTRAM = 1, MOVX @Ri and MOVX @DPTR will

be similar to the standard 8051. Using MOVX @Ri pro-

vides an 8-bit address with multiplexed data on Port 0.

Other output port pins can be used to output higher order

address bits. This provides external paging capabilities.

Using MOVX @DPTR generates a 16-bit address. This

allows external addressing up the 64K. Port 2 provides the

high-order eight address bits (DPH), and Port 0 multiplexes

the low order eight address bits (DPL) with data. Both

MOVX @Ri and MOVX @DPTR generates the necessary

©2007 Silicon Storage Technology, Inc.

13

S71255-08-000

1/07