OV5017 View Datasheet(PDF) - Omnivison Technologies

Part Name

Description

View to exact match

OV5017 Datasheet PDF : 20 Pages

| |||

OMNIVISION TECHNOLOGIES, Inc.

OV5017

Confidential Preliminary Product Specification

The Image Core is a complete analog video camera with 384 x 288 pixel size, which can run at full video

speed. The analog video signal complies with CCIR standards. At 50 fps, it may be too fast for many

applications; therefore, the frame rate or pixel rate can be programmed to match the external system

requirements. The on-chip 8-bit A/D can convert the video signal at 50 fps, and the conversion is syn-

chronized with the actual pixel rate.

The OV5017 also outputs standard timing reference signals such as VSYNC, HREF, PCLK. Databus is

shared by negating OEB.

The exposure control can be set to auto or manual operation. Automatic exposure computation is based

on full size image array and an exposure range over 100X. The AGC operation is tied to AEC in auto

operation. Therefore, use automatic exposure control when selecting full image size. Manual exposure

control allows individually adjusting exposure and gain based on actual application. Therefore, use man-

ual exposure time if the window is smaller than full size or if the target object is brighter or darker than

the average background.

The frame rate divider can achieve various frame rates on the fly without changing the input clock fre-

quency.

Single frame operation provides one frame data transfer by controlling the assertion of HREF for one

complete frame period. Setting FCTL(7) signals the control to assert the HREF in the next frame. Clear-

ing this bit before the new frame cancels the assertion of HREF.

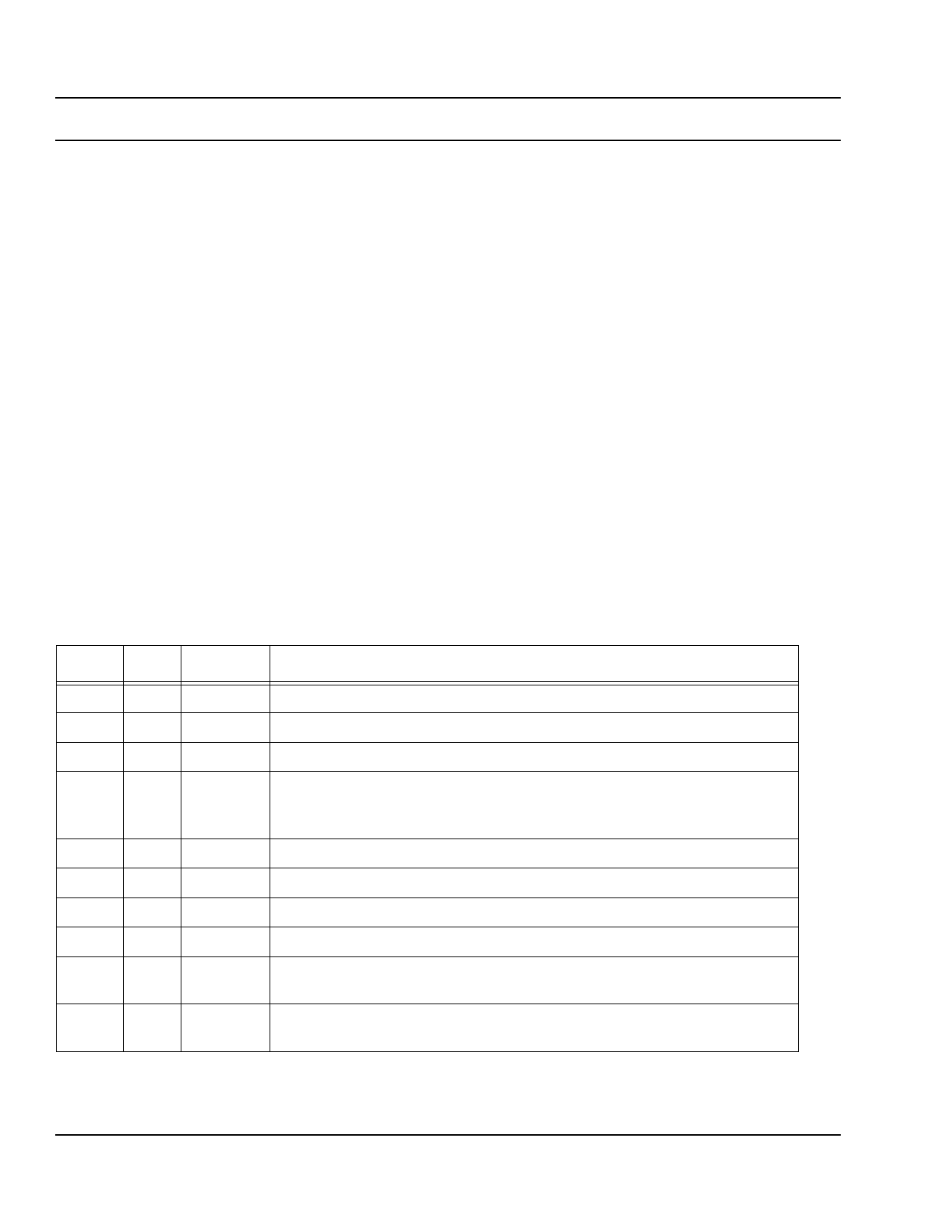

Table 1.Pin Descriptions

Pin # Class Pin Name

Description

1

Bias SGND

2

Bias SVDD

3

Bias AVDD

4

I-0

FSI

5

Bias

6

Bias

7

Bias

8-17

FT

18, 19, I

20, 46

21

I

VrCR

AGND

AGND

N/C

A3-A0

OEB

Sensor ground. Connect to supply common.

Sensor power (+5V) connection.

Analog power (+5V) connection.

External frame sync input. A rising edge on FSI sets the chip vertical sync timing.

For proper operation, the frequency of FSI must be half of the programmed frame

rate. Internally pulled down with a 100k resistor. Leave open or ground if unused.

Internal reference voltage. Requires a 0.1uF external capacitor to AGND.

Analog ground. Connect to supply common.

Analog ground. Connect to supply common.

Factory test. Leave open.

Address inputs for internal the registers. Requires CSB = 0 to access the registers.

Output enable for the eight bit data bus. OEB = 0 enables the data bus drivers.

OEB = 1 puts the data bus in tristate.

2

Version 1.6

October 20, 1997