May 2001

File Number

3108.3

# 12-Bit, Buffered, Multiplying CMOS DAC

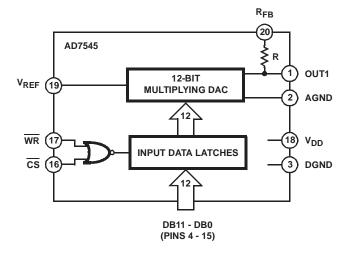

The AD7545 is a low cost monolithic 12-bit, CMOS multiplying DAC with on-board data latches. Data is loaded in a single 12-bit wide word which allows interfacing directly to most 12-bit and 16-bit bus systems. Loading of the input latches is under the control of the CS and WR inputs. A logic low on these control inputs makes the input latches transparent allowing direct unbuffered operation of the DAC.

#### Part Number Information

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE    | PKG.<br>NO. |

|-------------|---------------------|------------|-------------|

| AD7545JN    | 0 to 70             | 20 Ld PDIP | E20.3       |

| AD7545KN    | 0 to 70             | 20 Ld PDIP | E20.3       |

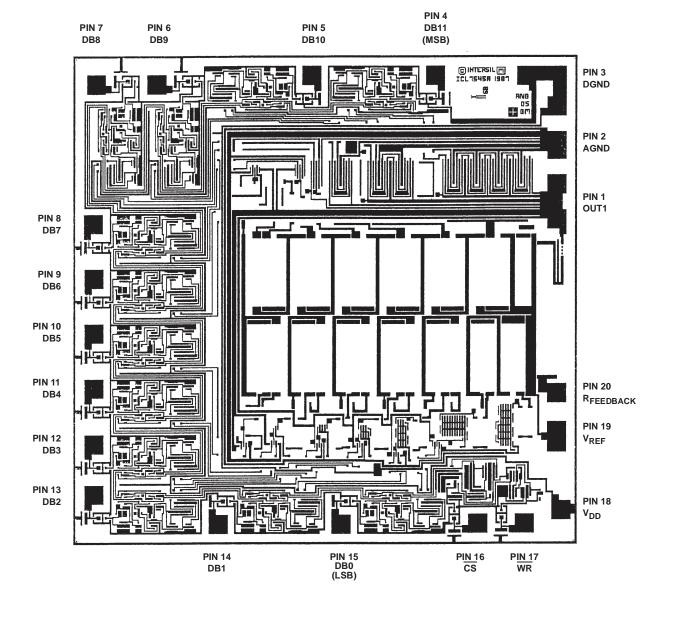

# Functional Diagram

#### **Features**

- 12-Bit Resolution

- Low Gain T.C. 2ppm/OC (Typ)

- Fast TTL/CMOS Compatible Data Latches

- Single +5V to +15V Supply

- Low Power

- Low Cost

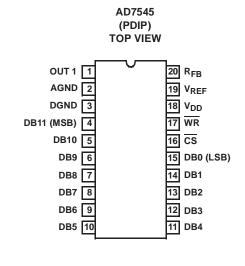

# **Pinout**

#### AD7545

# **Absolute Maximum Ratings**

#

# **Thermal Information**

| Thermal Resistance (Typical, Note 1)        | $\theta_{JA}$ (°C/W)                   |

|---------------------------------------------|----------------------------------------|

| PDIP Package                                | 80                                     |

| Maximum Junction Temperature (PDIP Package) |                                        |

| Maximum Storage Temperature Range68         | 5 <sup>0</sup> C to 150 <sup>0</sup> C |

| Maximum Lead Temperature (Soldering 10s)    | 300°C                                  |

# **Operating Conditions**

Temperature Range ......0°C to 70°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1. θ<sub>JA</sub> is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

# Electrical Specifications T<sub>A</sub> = See Note 2, V<sub>REF</sub> = +10V, V<sub>OUT1</sub> = 0V, AGND = DGND, Unless Otherwise Specified

| PARAMETER                                                                    |       |                                                                                                                                        | V <sub>DD</sub> = +5V (NOTE 7) |     |      | V <sub>DD</sub> = +15V (NOTE 7) |     |                     |                   |

|------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----|------|---------------------------------|-----|---------------------|-------------------|

|                                                                              |       | TEST CONDITIONS                                                                                                                        | MIN                            | TYP | MAX  | MIN                             | TYP | MAX                 | UNITS             |

| STATIC PERFORMANCE                                                           |       |                                                                                                                                        |                                |     | •    |                                 | 1   |                     |                   |

| Resolution                                                                   |       |                                                                                                                                        | 12                             | -   | -    | 12                              | -   | -                   | Bits              |

| Relative Accuracy                                                            | J     |                                                                                                                                        | -                              | -   | ±2   | -                               | -   | ±2                  | LSB               |

|                                                                              | K     |                                                                                                                                        | -                              | -   | ±1   | -                               | -   | ±1                  | LSB               |

| Differential Nonlinearity                                                    | J     | 10-Bit Monotonic T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                  | -                              | -   | ±4   | -                               | -   | ±4                  | LSB               |

|                                                                              | К     | 12-Bit Monotonic T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                  | -                              | -   | ±1   | -                               | -   | ±1                  | LSB               |

| Gain Error<br>(Using Internal RFB)                                           | J     | DAC Register Loaded with 1111 1111 1111                                                                                                | -                              | -   | ±20  | -                               | -   | ±25                 | LSB               |

|                                                                              | К     |                                                                                                                                        |                                | -   | ±15  | LSB                             |     |                     |                   |

| Gain Temperature Coeffici<br>ΔGain/ΔTemperature                              | ent   | Typical Value is 2ppm/ <sup>O</sup> C for V <sub>DD</sub> = +5V (Note 4)                                                               | -                              | -   | ±5   | - ±10                           |     | ppm/ <sup>o</sup> C |                   |

| DC Supply Rejection<br>ΔGain/ΔV <sub>DD</sub>                                |       | $\Delta V_{DD} = \pm 5\%$                                                                                                              | 0.015                          | -   | 0.03 | 0.01                            | -   | 0.02                | %                 |

| Output Leakage Current at J, K OUT1                                          |       | DB0 - DB11 = 0V; WR,<br>CS = 0V (Note 2)                                                                                               | -                              | -   | 50   | -                               | -   | 50                  | nA                |

| DYNAMIC CHARACTERIS                                                          | STICS | 1                                                                                                                                      |                                |     |      |                                 | 1   | ı                   | 1                 |

| Current Settling Time                                                        |       | To $^{1}/_{2}$ LSB, OUT1 LOAD = $100\Omega$ , DAC Output Measured from Falling Edge of $\overline{WR}$ , $\overline{CS} = 0V$ (Note 4) | -                              | -   | 2    | -                               | -   | 2                   | μs                |

| Propagation Delay from Digital Input<br>Change to 90% of Final Analog Output |       | OUT1 LOAD = $100\Omega$ ,<br>C <sub>EXT</sub> = $13$ pF (Notes 4 and 5)                                                                | -                              | -   | 300  | -                               | -   | 250                 | ns                |

| Digital to Analog Glitch Impu                                                | ılse  | V <sub>REF</sub> = AGND                                                                                                                | -                              | 400 | -    | -                               | 250 | -                   | nV/s              |

| AC Feedthrough at OUT1                                                       |       | V <sub>REF</sub> = ±10V, 10kHz Sinewave                                                                                                | -                              | 5   | -    | -                               | 5   | -                   | mV <sub>P-P</sub> |

| ANALOG OUTPUTS                                                               |       |                                                                                                                                        |                                |     |      | !                               | 1   | ļ.                  | '                 |

| Output Capacitance C <sub>OUT1</sub>                                         |       | $\frac{DB0 - DB11 = 0V,}{\overline{WR}, \overline{CS} = 0V \text{ (Note 4)}}$                                                          | -                              | -   | 70   | -                               | -   | 70                  | pF                |

|                                                                              |       | $\frac{DB0 - DB11 = V_{DD}}{WR, CS = 0V \text{ (Note 4)}}$                                                                             | -                              | -   | 200  | -                               | -   | 200                 | pF                |

**Electrical Specifications**  $T_A = See Note 2$ ,  $V_{REF} = +10V$ ,  $V_{OUT1} = 0V$ , AGND = DGND, Unless Otherwise Specified (Continued)

|                                     |                                                       | V <sub>DD</sub> | $V_{DD} = +5V \text{ (NOTE 7)}$ |     |     | V <sub>DD</sub> = +15V (NOTE 7) |      |       |

|-------------------------------------|-------------------------------------------------------|-----------------|---------------------------------|-----|-----|---------------------------------|------|-------|

| PARAMETER                           | TEST CONDITIONS                                       | MIN             | TYP                             | MAX | MIN | TYP                             | MAX  | UNITS |

| REFERENCE INPUT                     |                                                       | :               | •                               | •   | •   | •                               | •    |       |

| Input Resistance (Pin 19 to GND     | Input Resistance<br>TC = -300ppm/°C (Typ)             | 7               | -                               | -   | 7   | -                               | -    | kΩ    |

|                                     | Typical Input Resistance = 11kΩ                       | -               | -                               | 25  | -   | -                               | 25   | kΩ    |

| DIGITAL INPUTS                      |                                                       |                 |                                 |     |     |                                 |      |       |

| Input High Voltage, V <sub>IH</sub> |                                                       | 2.4             | -                               | -   | -   | -                               | 13.5 | V     |

| Input Low Voltage, V <sub>IL</sub>  |                                                       | -               | -                               | 0.8 | -   | -                               | 1.5  | V     |

| Input Current, I <sub>IN</sub>      | V <sub>IN</sub> = 0 or V <sub>DD</sub> (Note 6)       | ±1              | -                               | ±10 | ±1  | -                               | ±10  | μΑ    |

| Input Capacitance DB0 DB1           | IIN - ( /                                             | -               | -                               | 7   | -   | -                               | 7    | pF    |

| WR                                  | CS V <sub>IN</sub> = 0 (Note 4)                       | -               | -                               | 20  | -   | -                               | 20   | pF    |

| SWITCHING CHARACTERISTIC            | CS (Note 4)                                           |                 |                                 |     |     |                                 |      |       |

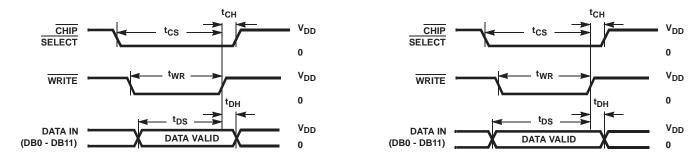

| Chip Select to Write Setup Time, t  | See Figure 1                                          | 380             | 200                             | -   | 200 | 120                             | -    | ns    |

| Chip Select to Write Hold Time,     | CH See Figure 1                                       | 0               | -                               | -   | 0   | -                               | -    | ns    |

| Write Pulse Width, tWR              | $t_{CS} \ge t_{WR}$ , $t_{CH} \ge 0$ , See Figure 1   | 400             | 175                             | -   | 240 | 100                             |      | ns    |

| Data Setup Time, t <sub>DS</sub>    | See Figure 1                                          | 210             | 100                             | -   | 120 | 60                              | -    | ns    |

| Data Hold Time, t <sub>DH</sub>     | See Figure 1                                          | 10              | -                               | -   | 10  | -                               | -    | ns    |

| POWER SUPPLY CHARACTER              | ISTICS                                                |                 |                                 |     |     | •                               | •    |       |

| I <sub>DD</sub>                     | All Digital Inputs V <sub>IL</sub> or V <sub>IH</sub> | -               | -                               | 2   | -   | -                               | 2    | mA    |

|                                     | All Digital Inputs 0V or V <sub>DD</sub>              | -               | 100                             | 500 | -   | 100                             | 500  | μΑ    |

|                                     | All Digital Inputs 0V or V <sub>DD</sub>              | -               | 10                              | -   | -   | 10                              | -    | μΑ    |

### NOTES:

- 2. Temperature Ranges as follows: J, K versions:  $0^{\circ}$ C to  $70^{\circ}$ C  $T_{A} = 25^{\circ}$ C for TYP Specifications. MIN and MAX are measured over the specified operating range.

- 3. This includes the effect of 5ppm maximum gain TC.

- 4. Parameter not tested. Parameter guaranteed by design, simulation, or characterization.

- 5. DB0 DB11 = 0V to  $V_{DD}$  or  $V_{DD}$  to 0V.

- 6. Logic inputs are MOS gates. Typical input current (25°C) is less than 1nA.

- 7. Typical values are not guaranteed but reflect mean performance specification. Specifications subject to change without notice.

# **Timing Diagrams**

FIGURE 1A. TYPICAL WRITE CYCLE

3

FIGURE 1B. PREFERRED WRITE CYCLE

FIGURE 1. WRITE CYCLE TIMING DIAGRAM

| MODE SELECTION                                              |  |  |  |  |  |

|-------------------------------------------------------------|--|--|--|--|--|

| CS and WR low, DAC responds to data bus (DB0 - DB11) inputs |  |  |  |  |  |

#### NOTES:

- 8.  $V_{DD} = +5V$ ;  $t_r = t_f = 20$ ns.

- 9.  $V_{DD} = +15V$ ;  $t_r = t_f = 40$ ns.

- 10. All input signal rise and fall times measured from 10% to 90% of  $\ensuremath{V_{DD}}.$

- 11. Timing measurement reference level is (V<sub>IH</sub> + V<sub>IL</sub>)/2.

- 12. Since input data latches are transparent for CS and WR both low, it is preferred to have data valid before CS and WR both go low. This prevents undesirable changes at the analog output while the data inputs settle.

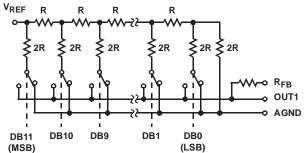

### Circuit Information - D/A Converter Section

Figure 2 shows a simplified circuit of the D/A converter section of the AD7545. Note that the ladder termination resistor is connected to AGND. R is typically  $11k\Omega$ .

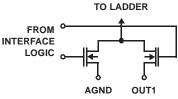

The binary weighted currents are switched between the OUT1 bus line and AGND by N-Channel switches, thus maintaining a constant current in each ladder leg independent of the switch state. One of the current switches is shown in Figure 3.

FIGURE 2. SIMPLIFIED D/A CIRCUIT OF AD7545

FIGURE 3. N-CHANNEL CURRENT STEERING SWITCH

The capacitance at the OUT1 bus line,  $C_{OUT1}$ , is code dependent and varies from 70pF (all switches to AGND) to 200pF (all switches to OUT1).

The input resistance at  $V_{REF}$  (Figure 2) is always equal to  $R_{LDR}$  ( $R_{LDR}$  is the R/2R ladder characteristic resistance and is equal to the value "R"). Since  $R_{IN}$  at the  $V_{REF}$  pin is constant, the reference terminal can be driven by a reference voltage or a reference current, AC or DC, of positive or negative polarity. (If a current source is used, a low temperature coefficient external  $R_{FB}$  is recommended to define scale factor).

# Circuit Information - Digital Section

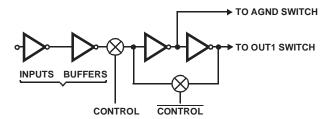

Figure 4 shows the digital structure for one bit. The digital signals CONTROL and  $\overline{\text{CONTROL}}$  are generated from  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$ .

FIGURE 4. DIGITAL INPUT STRUCTURE

The input buffers are simple CMOS inverters designed such that when the AD7545 is operated with  $V_{DD} = 5V$ , the buffers convert TTL input levels (2.4V and 0.8V) into CMOS logic levels. When  $V_{IN}$  is in the region of 2.0V to 3.5V the input buffers operate in their linear region and draw current from the power supply. To minimize power supply currents it is recommended that the digital input voltages be as close to the supply rails ( $V_{DD}$  and DGND) as is practically possible.

The AD7545 may be operated with any supply voltage in the range  $5V \le V_{DD} \le 15V$ . With  $V_{DD} = +15V$  the input logic levels are CMOS compatible only, i.e., 1.5V and 13.5V.

# **Application**

#### **Output Offset**

CMOS current-steering D/A converters exhibit a code dependent output resistance which in turn causes a code dependent amplifier noise gain. The effect is a code dependent differential nonlinearity term at the amplifier output which depends on  $V_{OS}$  where  $V_{OS}$  is the amplifier input offset voltage. To maintain monotonic operation it is recommended that  $V_{OS}$  be no greater than (25 x 10<sup>-6</sup>) ( $V_{RFF}$ ) over the temperature range of operation.

#### General Ground Management

AC or transient voltages between AGND and DGND can cause noise injection into the analog output. The simplest method of ensuring that voltages at AGND and DGND are equal is to tie AGND and DGND together at the AD7545. In more complex systems where the AGND and DGND connection is on the backplane, it is recommended that two diodes be connected in inverse parallel between the AD7545 AGND and DGND pins (1N914 or equivalent).

# **Digital Glitches**

When  $\overline{\text{WR}}$  and  $\overline{\text{CS}}$  are both low the latched are transparent and the D/A converter inputs follow the data inputs. In some bus systems, data on the data bus is not always valid for the whole period during which  $\overline{\text{WR}}$  is low and as a result invalid data can briefly occur at the D/A converter inputs during a write cycle. Such invalid data can cause unwanted glitches at the output of the D/A converter. The solution to this

problem, if it occurs, is to retime the write pulse  $(\overline{WR})$  so that it only occurs when data is valid.

Another cause of digital glitches is capacitive coupling from the digital lines to the OUT1 and AGND terminals. This should be minimized by isolating the analog pins of the AD7545 (pins 1, 2, 19, 20) from the digital pins by a ground track run between pins 2 and 3 and between pins 18 and 19 of the AD7545. Note how the analog pins are at one end of the package and separated from the digital pins by  $V_{DD}$  and DGND to aid isolation at the board level. On-chip capacitive coupling can also give rise to crosstalk from the digital to analog sections of the AD7545, particularly in circuits with high currents and fast rise and fall times. This type of crosstalk is minimized by using  $V_{DD} = +5V$ . However, great care should be taken to ensure that the +5V used to power the AD7545 is free from digitally induced noise.

#### **Temperature Coefficients**

The gain temperature coefficient of the AD7545 has a maximum value of 5ppm/°C and a typical value of 2ppm/°C. This corresponds to worst case gain shifts of 2 LSBs and 0.8 LSBs respectively over a 100°C temperature range. When trim resistors R1 and R2 are used to adjust full scale range, the temperature coefficient of R1 and R2 should also be taken into account.

# **Basic Applications**

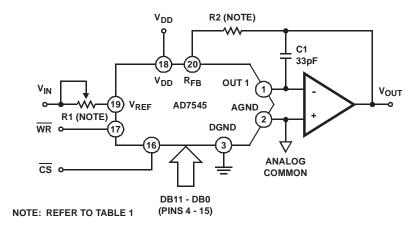

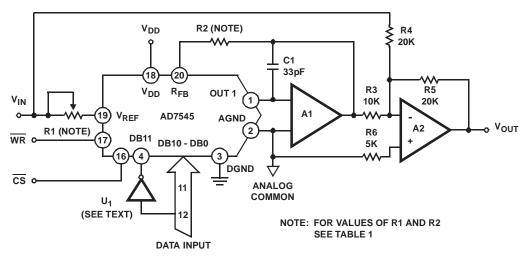

Figures 5 and 6 show simple unipolar and bipolar circuits using the AD7545. Resistor R1 is used to trim for full scale. Capacitor C1 provides phase compensation and helps prevent overshoot and ringing when using high speed op amps. Note that the circuits of Figures 5 and 6 have constant input impedance at the  $V_{REF}$  terminal.

The circuit of Figure 5 can either be used as a fixed reference D/A converter so that it provides an analog output voltage in the range 0V to -V<sub>IN</sub> (note the inversion introduced by the op amp) or V<sub>IN</sub> can be an AC signal in which case the circuit behaves as an attenuator (2-Quadrant Multiplier). V<sub>IN</sub> can be any voltage in the range -20V  $\leq$  V<sub>IN</sub>  $\leq$  +20V (provided the op amp can handle such voltages) since V<sub>REF</sub> is permitted to exceed V<sub>DD</sub>. Table 2 shows the code relationship for the circuit of Figure 5.

Figure 6 and Table 3 illustrate the recommended circuit and code relationship for bipolar operation. The D/A function itself uses offset binary code and inverter U<sub>1</sub> on the MSB line converts 2's complement input code to offset binary code. If appropriate, inversion of the MSB may be done in software using an exclusive -OR instruction and the inverter omitted. R3, R4 and R5 must be selected to match within 0.01% and they should be the same type of resistor (preferably wire-wound or metal foil), so that their temperature coefficients match. Mismatch of R3 value to R4 causes both offset and full scale error. Mismatch of R5 to R4 and R3 causes full scale error.

The choice of the operational amplifiers in Figure 5 and Figure 6 depends on the application and the trade off between required precision and speed. Below is a list of

operational amplifiers which are good candidates for many applications. The main selection criteria for these operational amplifiers is to have low  $V_{OS}$ , low  $V_{OS}$  drift, low bias current and low settling time.

These amplifiers need to maintain the low nonlinearity and monotonic operation of the D/A while providing enough speed for maximum converter performance.

# **Operational Amplifiers**

HA-5127 Ultra Low Noise, Precision

HA-5137 Ultra Low Noise, Precision, Wide Band

HA-5147 Ultra Low Noise, Precision, High Slew Rate

HA-5170 Precision, JFET Input

TABLE 1. RECOMMENDED TRIM RESISTOR VALUES vs GRADES FOR  $V_{DD}$  = +5V

| TRIM RESISTOR | J           | K    |

|---------------|-------------|------|

| R1            | $500\Omega$ | 200Ω |

| R2            | 150Ω        | 68Ω  |

TABLE 2. UNIPOLAR BINARY CODE TABLE FOR CIRCUIT OF FIGURE 5

| BINARY | / NUMBER<br>REGISTER | IN DAC | ANALOG OUTPUT                                                      |

|--------|----------------------|--------|--------------------------------------------------------------------|

| 1111   | 1111                 | 1111   | $-V_{IN} \left\{ \frac{4095}{4096} \right\}$                       |

| 1000   | 0000                 | 0000   | $-V_{IN} \left\{ \frac{2048}{4096} \right\} = -\frac{1}{2} V_{IN}$ |

| 0000   | 0000                 | 0001   | $-V_{IN}\left\{\frac{1}{4096}\right\}$                             |

| 0000   | 0000                 | 0000   | 0V                                                                 |

TABLE 3. 2'S COMPLEMENT CODE TABLE FOR CIRCUIT OF FIGURE 6

| Г    | DATA INPU | Т    | ANALOG OUTPUT                                        |

|------|-----------|------|------------------------------------------------------|

| 0111 | 1111      | 1111 | $+V_{IN} \cdot \left\{ \frac{2047}{2048} \right\}$   |

| 0000 | 0000      | 0001 | $+V_{IN} \bullet \left\{ \frac{1}{2048} \right\}$    |

| 0000 | 0000      | 0000 | 0V                                                   |

| 1111 | 1111      | 1111 | $-V_{IN} \bullet \left\{ \frac{1}{2048} \right\}$    |

| 1000 | 0000      | 0000 | $-V_{1N} \bullet \left\{ \frac{2048}{2048} \right\}$ |

FIGURE 5. UNIPOLAR BINARY OPERATION

FIGURE 6. BIPOLAR OPERATION (2'S COMPLEMENT CODE)

# Die Characteristics

# **DIE DIMENSIONS**

121 mils x 123 mils (3073μm x 3124μm)

# **METALLIZATION**

Type: Pure Aluminum Thickness: 10±1kÅ

# **PASSIVATION**

Type: PSG/Nitride PSG: 7 ±1.4kÅ Nitride: 8 ±1.2kÅ

### **PROCESS**

**CMOS Metal Gate**

# Metallization Mask Layout

#### AD7545

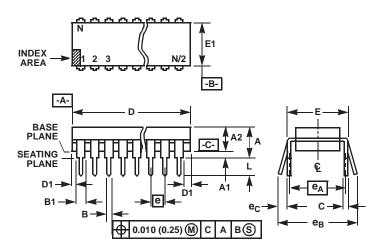

# Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C-.

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

E20.3 (JEDEC MS-001-AD ISSUE D)

20 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INC   | HES   | MILLIM   |          |       |

|----------------|-------|-------|----------|----------|-------|

| SYMBOL         | MIN   | MAX   | MIN      | MAX      | NOTES |

| А              | -     | 0.210 | -        | 5.33     | 4     |

| A1             | 0.015 | -     | 0.39     | -        | 4     |

| A2             | 0.115 | 0.195 | 2.93     | 4.95     | -     |

| В              | 0.014 | 0.022 | 0.356    | 0.558    | -     |

| B1             | 0.045 | 0.070 | 1.55     | 1.77     | 8     |

| С              | 0.008 | 0.014 | 0.204    | 0.355    | -     |

| D              | 0.980 | 1.060 | 24.89    | 26.9     | 5     |

| D1             | 0.005 | -     | 0.13     | -        | 5     |

| Е              | 0.300 | 0.325 | 7.62     | 8.25     | 6     |

| E1             | 0.240 | 0.280 | 6.10     | 7.11     | 5     |

| е              | 0.100 | BSC   | 2.54     | 2.54 BSC |       |

| e <sub>A</sub> | 0.300 | BSC   | 7.62 BSC |          | 6     |

| e <sub>B</sub> | -     | 0.430 | -        | 10.92    | 7     |

| L              | 0.115 | 0.150 | 2.93     | 3.81     | 4     |

| N              | 2     | 0     | 2        | 9        |       |

Rev. 0 12/93

All Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at website <a href="https://www.intersil.com/design/quality/iso.asp">www.intersil.com/design/quality/iso.asp</a>.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com

# Sales Office Headquarters

NORTH AMERICA Intersil Corporation 2401 Palm Bay Rd. Palm Bay, FL 32905 TEL: (321) 724-7000 FAX: (321) 724-7240 EUROPE Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

ASIA Intersil Ltd.

Republic of China

TEL: 886-2-2515-8508 FAX: 886-2-2515-8369