PD- 93844B

**Dual FETKY™**

## International **167** Rectifier

# IRF7901D1

- Co-Pack Dual N-channel HEXFET<sup>®</sup> Power MOSFET and Schottky Diode

- Ideal for Synchronous Buck DC-DC Converters Up to 5A Peak Output

- Low Conduction Losses

- Low Switching Losses

- · Low Vf Schottky Rectifier

|                     | Q1      | Q2           |

|---------------------|---------|--------------|

|                     |         | and Schottky |

| V <sub>DS</sub>     | 30V     | 30V          |

| R <sub>DS(on)</sub> | 38 mΩ   | 32 mΩ        |

| Q <sub>G</sub>      | 10.5 nC | 18.3 nC      |

| $Q_{sw}$            | 3.8 nC  | 9.0 nC       |

| $V_{\rm SD}$        | 1.0V    | 0.52V        |

Device Ratings (Max.Values)

**Co-Packaged Dual MOSFET Plus Schottky Diode**

#### Description

The FETKY<sup>™</sup> family of Co-Pack HEXFET<sup>®</sup>MOSFETs and Schottky diodes offers the designer an innovative, board space saving solution for switching regulator and power management applications. Advanced HEXFET<sup>®</sup>MOSFETs combined with low forward drop Schottky results in an extremely efficient device suitable for a wide variety of portable electronics applications.

The SO-8 has been modified through a customized leadframe for enhanced thermal characteristics and multiple die capability making it ideal in a variety of power applications. With these improvements, multiple devices can be used in an application with dramatically reduced board space. Internal connections enable easier board layout design with reduced stray inductance.

#### **Absolute Maximum Ratings**

| Parameter                              |                        | Symbol               | IRF7901D1  | Units |

|----------------------------------------|------------------------|----------------------|------------|-------|

| Drain-Source Voltage                   |                        | V <sub>DS</sub>      | 30         | V     |

| Gate-Source Voltage                    |                        | $V_{gs}$             | ±20        |       |

| Continuous Output $T_1 = 100^{\circ}C$ |                        | I <sub>D</sub>       | 6.2        | А     |

| Current ( $V_{GS} \ge 4.5V$ ) (4)      |                        |                      |            |       |

| Pulsed Drain Current <sup>①</sup>      |                        | I <sub>DM</sub>      | 24         | *     |

| Power Dissipation3                     | $T_{L} = 100^{\circ}C$ | P <sub>D</sub>       | 2.0        | W     |

| Junction & Storage Temperate           | ure Range              | T_, T <sub>stg</sub> | -55 to 150 | °C    |

| Pulsed Source Current ①                |                        | I <sub>sm</sub>      | 12         | А     |

#### **Thermal Resistance**

| Parameter                    |                  | Max. | Units |

|------------------------------|------------------|------|-------|

| Maximum Junction-to-Ambient3 | R <sub>eja</sub> | 62.5 | °C/W  |

| Maximum Junction-to-Lead®    | R <sub>ejl</sub> | 25   | °C/W  |

| wayay inf ago                | *                | •    | 4     |

### International **TOR** Rectifier

| Electrical Characteristics             |                      | Q1 - Control FET |      |      | Q2 - Synch FET<br>& Schottky |      |      |       |                                                                |

|----------------------------------------|----------------------|------------------|------|------|------------------------------|------|------|-------|----------------------------------------------------------------|

| Parameter                              |                      | Min              | Тур  | Max  | Min                          | Тур  | Max  | Units | Conditions                                                     |

| Drain-to-Source<br>Breakdown Voltage*  | $BV_{DSS}$           | 30               | -    | -    | 30                           | -    | -    | V     | $V_{GS} = 0V, I_{D} = 250 \mu A$                               |

| Static Drain-Source<br>on Resistance*  | R <sub>DS</sub> (on) | _                | 28   | 38   | -                            | 23   | 32   | mΩ    | $V_{GS} = 4.5V, I_{D} = 5A^{2}$                                |

| Gate Threshold Voltage*                | V <sub>GS</sub> (th) | 1.0              | -    | -    | 1.0                          | -    | -    | V     | $V_{\rm DS} = V_{\rm GS}, I_{\rm D} = 250 \mu A$               |

| Drain-Source Leakage                   | I <sub>DSS</sub>     | -                | -    | 30   | -                            | -    | 30   | μA    | $V_{\rm DS} = 24 V, V_{\rm GS} = 0$                            |

|                                        |                      | _                | -    | 0.15 | _                            | _    | 4.3  | mA    | $V_{\rm DS} = 24 V, V_{\rm GS} = 0, T_{\rm J} = 125^{\circ} C$ |

| Gate-Source Leakage<br>Current*        | I <sub>GSS</sub>     | -                | -    | ±100 | _                            | -    | ±100 | nA    | $V_{GS} = \pm 20V$                                             |

| Total Gate Charge*                     | Q <sub>G cont</sub>  | -                | 7.6  | 10.5 | -                            | 15.5 | 21.0 |       | $V_{GS} = 5V, V_{DS} = 16V, I_{D} = 5A$                        |

|                                        | Q <sub>G synch</sub> | -                | 6.7  | 9.0  | _                            | 13.5 | 18.3 |       | $V_{gs} = 5V, V_{Ds} = 100 \text{mV}, I_{D} = 5\text{A}$       |

| Pre-Vth<br>Gate-Source Charge          | Q <sub>GS1</sub>     | -                | 2.0  | -    | -                            | 5.5  | -    |       | $V_{DS} = 16V, I_{D} = 5A$                                     |

| Post-Vth<br>Gate-Source Charge         | Q <sub>GS2</sub>     | -                | 0.5  | -    | -                            | 0.9  | -    | nC    |                                                                |

| Gate to Drain Charge                   | $Q_{_{\mathrm{GD}}}$ | -                | 1.9  | -    | _                            | 4.7  | -    |       |                                                                |

| Switch Charge*<br>$(Q_{gs2} + Q_{gd})$ | Q <sub>sw</sub>      | -                | 2.4  | 3.8  | -                            | 5.6  | 9.0  |       |                                                                |

| Output Charge*                         | Q <sub>oss</sub>     | -                | 13.5 | 18.0 | _                            | 9.0  | 12.3 |       | $V_{DS} = 16V, V_{GS} = 0$                                     |

| Gate Resistance                        | R <sub>G</sub>       | -                | 3.4  | -    | -                            | 4.3  | -    | Ω     |                                                                |

| Input Capacitance                      | C <sub>iss</sub>     | -                | 780  | -    | -                            | 1810 | -    |       |                                                                |

| Output Capacitance                     | C <sub>oss</sub>     | -                | 430  | -    | _                            | 310  | -    | pF    | $V_{_{DS}} = 16V, V_{_{GS}} = 0, f = 1MHz$                     |

| Transfer Capacitance                   | C <sub>rss</sub>     | -                | 30   | -    | _                            | 110  | -    |       |                                                                |

| Turn-On Delay Time                     | t <sub>d</sub> (on)  | -                | 7.2  | -    | -                            | 10.4 | -    |       | $V_{DD} = 16V, I_{D} = 5A, V_{GS} = 5V$                        |

| RiseTime                               | t,                   | -                | 13.8 | -    | _                            | 16.4 | -    | ns    | Clamped inductive load                                         |

| Turn-Off Delay Time                    | t <sub>d</sub> (off) | -                | 14.7 | -    | _                            | 14.6 | -    |       | See test diagram Fig 17.                                       |

| FallTime                               | t <sub>r</sub>       | -                | 8    | -    | _                            | 5.2  | -    |       |                                                                |

**Source-Drain Ratings and Characteristics**

|                            |                 |     | Q1   |     | Q2 & parallel Schottky |      |      |       |                                                            |  |

|----------------------------|-----------------|-----|------|-----|------------------------|------|------|-------|------------------------------------------------------------|--|

| Parameter                  |                 | Min | Тур  | Max | Min                    | Тур  | Max  | Units | Conditions                                                 |  |

| Diode Forward<br>Voltage*② | V <sub>SD</sub> | -   | 0.7  | 1.0 | _                      | 0.48 | 0.52 | V     | $I_{s} = 1A, V_{gs} = 0V$                                  |  |

| Reverse Recovery<br>Charge | Q <sub>r</sub>  | -   | 62.3 | -   | -                      | 8.9  | -    | nC    | dI/dt = 700A/us<br>$V_{DS} = 16V, V_{GS} = 0V, I_{S} = 5A$ |  |

Repetitive rating; pulse width limited by max. junction temperature. Pulse width  $\leq$  300 µs; duty cycle  $\leq$  2%. When mounted on 1 inch square copper board, t < 10 sec. 1

Combined Q1, Q2 I<sub>RMS</sub> @ Pwr V<sub>out</sub> pins. Calculated continuous current based on maximum allowable junction temperature; switching or other losses will decrease RMS current capability When mounted on IRNBPS2 design kit. Measured as device T<sub>j</sub> to Pwr leads (V<sub>in</sub> & V<sub>out</sub>) Devices are 100% tested to these parameters. 4 (5)

\*

<sup>2</sup> 3

International **TOR** Rectifier

### IRF7901D1

#### Power MOSFET Optimization for DC-DC Converters

Table 1 and Table 2 describes the event during the various charge segments and shows an approximation of losses during that period.

|                    | Description                                                                                                                                                                                     | Segment Losses                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conduction<br>Loss | Losses associated with MOSFET on time. I <sub>RMS</sub> is a function of load current and duty cycle.                                                                                           | $P_{COND} = I_{RMS}^{2} \times R_{DS(on)}$                                                                                                                                                                                                                                                                                                                                                                    |

| Gate Drive<br>Loss | Losses associated with charging and discharging the gate of the MOSFET every cycle. Use the control FET $Q_{g}$ .                                                                               | $\mathbf{P}_{\mathrm{IN}} = \mathbf{V}_{\mathrm{G}} \times \mathbf{Q}_{\mathrm{G}} \times f$                                                                                                                                                                                                                                                                                                                  |

| Switching<br>Loss  | Losses during the drain voltage and drain current transitions for every full cycle.<br>Losses occur during the $Q_{GS2}$ and $Q_{GD}$ time period and can be simplified by using $Q_{switch}$ . | $\begin{split} \mathbf{P}_{QGS2} &\approx \mathbf{V}_{IN} \times \mathbf{I}_{L} \times \frac{\mathbf{Q}_{GS2}}{\mathbf{I}_{G}} \times \mathbf{J} \\ \mathbf{P}_{QGD} &\approx \mathbf{V}_{IN} \times \mathbf{I}_{L} \times \frac{\mathbf{Q}_{GD}}{\mathbf{I}_{G}} \times f \\ \mathbf{P}_{SWITCH} &\approx \mathbf{V}_{IN} \times \mathbf{I}_{L} \frac{\mathbf{Q}_{SW}}{\mathbf{I}_{G}} \times f \end{split}$ |

| Output<br>Loss     | Losses associated with the $Q_{oss}$ of the device every cycle when the control FET turns on. Losses are caused by both FETs, but are dissipated by the control FET.                            | $P_{OUTPUT} = \frac{Q_{OSS}}{2} \times V_{IN} \times f$                                                                                                                                                                                                                                                                                                                                                       |

|                    | Table 2 – Synchronous FET Losses                                                                                                                                                    |                                                                                                                                                                                |  |  |  |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                    | Description                                                                                                                                                                         | Segment Losses                                                                                                                                                                 |  |  |  |  |  |  |

| Conduction<br>Loss | Losses associated with MOSFET on time. I <sub>RMS</sub> is a function of load current and duty cycle.                                                                               | $P_{COND} = I_{RMS}^{2} \times R_{DSon}$                                                                                                                                       |  |  |  |  |  |  |

| Gate Drive<br>Loss | Losses associated with charging and discharging the gate of the MOSFET every cycle. Use the Sync FET $Q_c$ .                                                                        | $\mathbf{P}_{\mathrm{IN}} = \mathbf{V}_{\mathrm{G}} \times \mathbf{Q}_{\mathrm{G}} \times f$                                                                                   |  |  |  |  |  |  |

| Switching<br>Loss  |                                                                                                                                                                                     | $\begin{aligned} \mathbf{P}_{\text{SWITCH}} &\approx 0 \\ \mathbf{P}_{\text{OUTPUT}} = \frac{\mathbf{Q}_{\text{OSS}}}{2} \times \mathbf{V}_{\text{IN}} \times f \end{aligned}$ |  |  |  |  |  |  |

| Output<br>Loss     | Losses associated with the Q <sub>oss</sub> of the device every cycle when the control FET turns on. They are caused by the synchronous FET, but are dissipated in the control FET. |                                                                                                                                                                                |  |  |  |  |  |  |

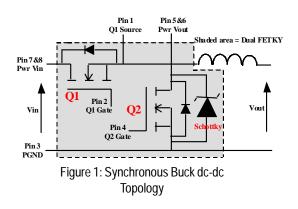

#### **Typical Application**

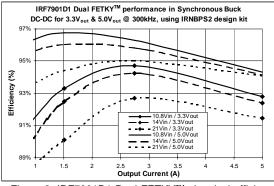

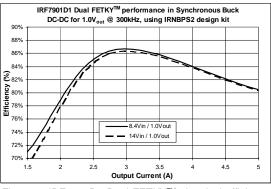

The performance of the new Dual FETKY<sup>TM</sup> has been tested in-circuit using IR's new IRNBPS2 "Dual Output Synchronous Buck Design Kit", operating up to  $21V_{in}$  and 5A peak output current, with operating voltages from  $1V_{out}$  to  $5V_{out}$ .

#### **Typical Application (Contd.)**

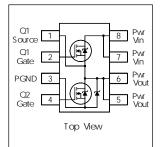

The Dual FETKY integrates all the power semiconductor devices for DC-DC conversion within one SO-8 package, as shown on page 1. The high side control MOSFET (Q1) is optimized for low combined  $Q_{sw}$  and  $R_{DS}(on)$ . The low side synchronous MOSFET (Q2) is optimized for low  $R_{DS}(on)$  and high Cdv/dt immunity. The ultra-low  $V_f$  schottky diode is internally connected in parallel with the synchronous MOSFET, for improved deadtime efficiency. For ease of circuit board layout, the Dual FETKY has been internally configured such that it represents a functional block for the power device portion of the synchronous buck DC-DC converter. This helps to minimize the external PCB traces compared to a discrete solution.

#### **In-Circuit Efficiency**

The in-circuit efficiency curves for the Dual FETKY are shown in Figure 2 & 3. The Dual FETKY can achieve up to 96.6% and 94.6% peak efficiency for the 5.0V and 3.3V applications respectively, with excellent maximum load efficiency.

International **TOR** Rectifier

### IRF7901D1

International

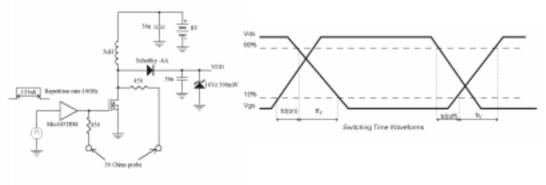

Figure 17. Clamped Inductive Load Test Diagram and Switching waveform.

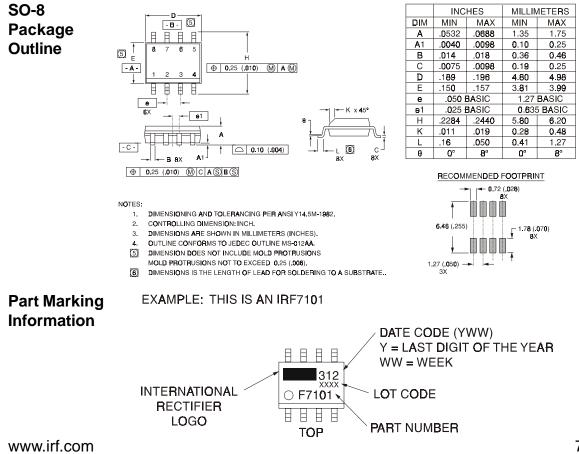

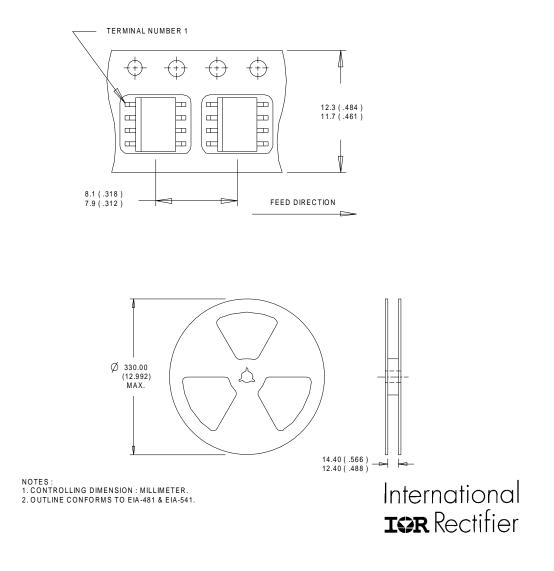

#### SO-8 Tape & Reel Information

Dimensions are shown in millimeters (inches)

Data and specifications subject to change without notice. This product has been designed and qualified for the consumer market. Qualification Standards can be found on IR's Web site.

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105 TAC Fax: (310) 252-7903 Visit us at www.irf.com for sales contact informatin.9/01