PDI1394L21 View Datasheet(PDF) - Philips Electronics

Part Name

Description

View to exact match

PDI1394L21 Datasheet PDF : 52 Pages

| |||

Philips Semiconductors

1394 full duplex AV link layer controller

Preliminary specification

PDI1394L21

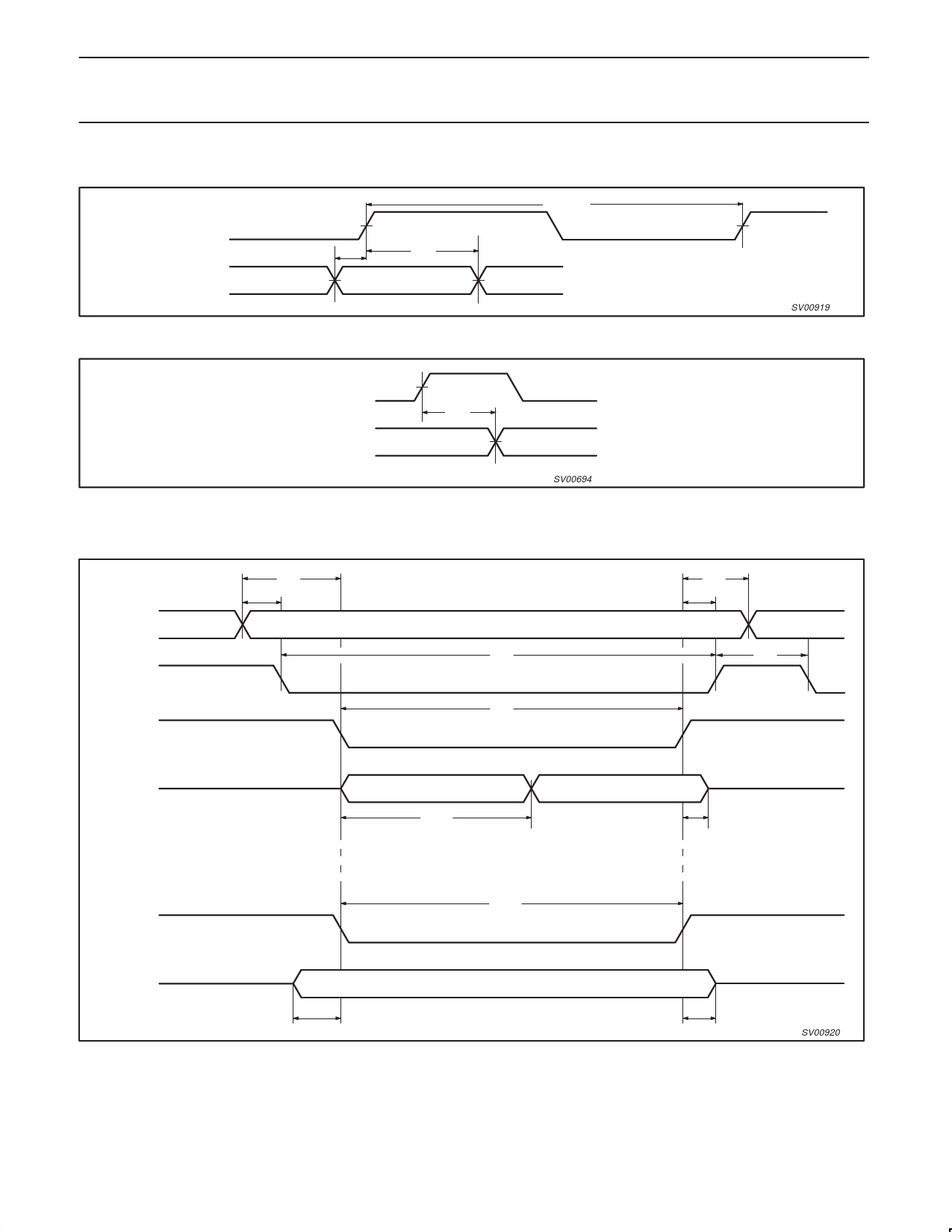

16.3 PHY-Link Interface Critical Timings

SCLK

PHY D[0:7], PHY CTL[0:1]

50%

tSUP

tHP

50%

tSCLKPER

50%

Figure 28. PHY D[0:7], PHY CTL[0:1] Input Setup and Hold Timing Waveforms

50%

SV00919

SCLK

PHY D[0:7], PHY CTL[0:1], LREQ

50%

tDP

50%

SV00694

Figure 29. PHY D[0:7], PHY CTL[0:1], and LREQ Output-Delay Timing Waveforms

16.4 Host Interface Critical Timings

READ

tAS

tAS

HIF A[8:0]

VALID

tCL

HIF CS_N

tRP

HIF RD_N

HIF D[7:0]

ÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉ

tACC

tAH

tAH

tCH

VALID

tDZ

WRITE

HIF WR_N

tWRP

HIF D[7:0]

VALID

tDS

tDH

Figure 30. Host Interface Timing Waveforms

SV00920

1999 Aug 06

47